# TLE9471ES

## Lite CAN SBC Family

## 1 Overview

### **Features**

### **Key Features**

- Very low quiescent current consumption in Stop- and Sleep Mode

- Periodic Cyclic Wake in SBC Normal-, Stop- and Sleep Mode

- Periodic Cyclic Sense in SBC Normal-, Stop- and Sleep Mode

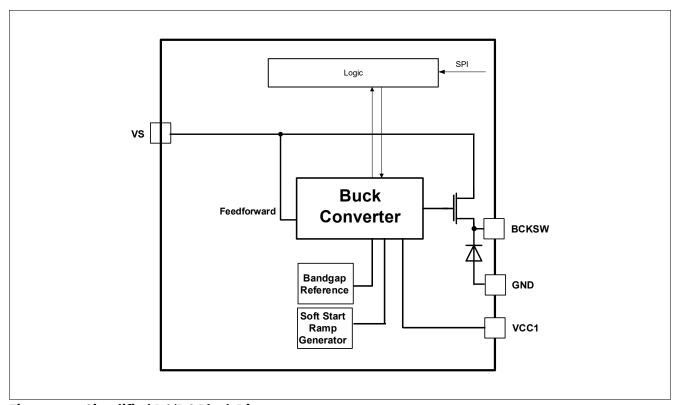

- Low-Drop Buck DC/DC Voltage Regulator 5 V, 500 mA for main supply with integrated spread spectrum modulation feature for optimum EMC performance

- Low-Drop Linear Voltage Regulator 5 V, 100 mA, protection feature for off-board usage

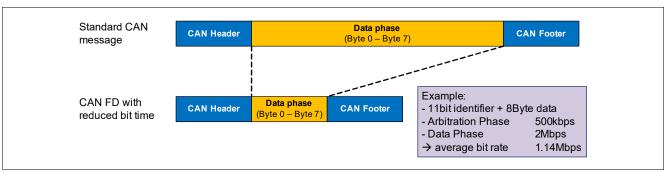

- High-Speed CAN transceiver supporting FD communication up to 5 Mbit/s according to ISO 11898-2:2016

& SAE J2284

- Fully compliant to "Hardware Requirements for LIN, CAN and FlexRay Interfaces in Automotive Applications" Revision 1.3, 2012-05-04

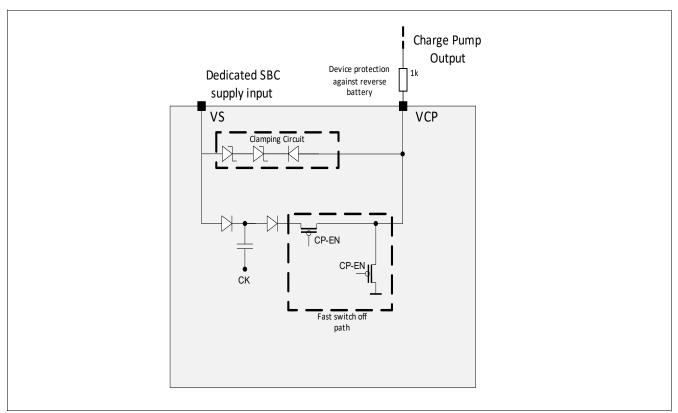

- Charge pump-output for N-channel MOSFET reverse-polarity protection or load switch feature with integrated spread spectrum modulation feature for optimum EMC performance

- Universal High-Voltage Wake input for voltage level monitoring and wake-up detection

- General Purpose High-Voltage in- and output (GPIO) configurable as Fail Output, Wake Input, Low-Side switch or High-Side switch

- · High-Voltage Measurement function as alternative pin assignment

- Fail Output for Fail-Safe signalization

- Configurable wake-up sources

- Reset & Interrupt outputs

- · Configurable timeout and window watchdog

- Overtemperature and short circuit protection feature

- Dedicated TEST pin for SBC Development Mode entry (watchdog counter stopped)

- Software compatible to other SBC families TLE926x and TLE927x

- Wide input voltage and temperature range

- Optimized for Electromagnetic Compatibility (EMC) and low Electromagnetic Emission (EME)

- Optimized for high immunity against Electromagnetic Interference (EMI)

- AEC Qualified & Green Product (RoHS compliant)

# **(infineon**

#### **Overview**

### Scalable System Basis Chip (SBC) Family

- Product family for complete scalable application coverage

- Optimized feature set for optimal system design

- Dedicated Data Sheets are available for all product variants

- Complete compatibility (hardware- and software across the family)

- Same PG-TSDSO-24-1 package with exposed pad (EP) for all product variants

- CAN Partial Networking variants (-3ES)

- Product variants for 5 V (TLE94xxyy) and 3.3 V (TLE94xxyyV33) output voltage for main regulator

- Software compatible to other SBC families TLE926x and TLE927x

## **Potential applications**

- In-Cabin Wireless Charger

- · Transmission, Transfer Case, Gear shifter and selectors

- Exhaust module and NOx sensor

- Water pump

- Wiper

- HVAC ECU and Control panel

- · Light Control Unit (LCU) for front, rear and ambient

- Seat belt pretension

- Steering column and steering lock

### **Product validation**

Qualified for automotive applications. Product validation according to AEC-Q100/101.

# **Description**

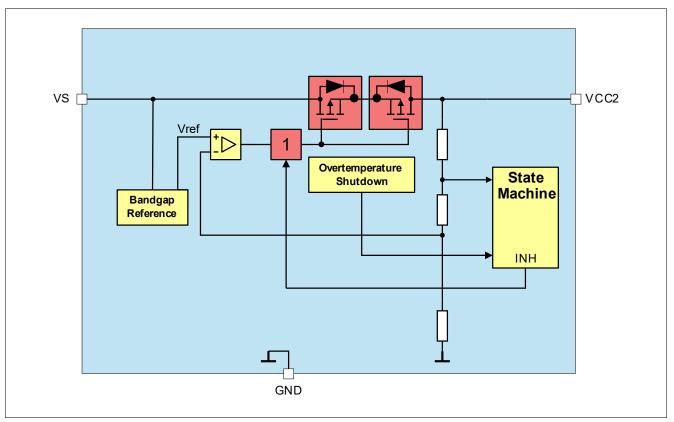

The TLE9471ES is a monolithically integrated circuit in an exposed pad PG-TSDSO-24-1 (150 mil) power package. The device is designed for various CAN automotive applications as main supply for the microcontroller and as interface for a CAN bus network.

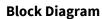

To support these applications, the System Basis Chip (SBC) provides the main functions, such as a 5 V low-dropout voltage regulator (Buck SMPS) for e.g. a microcontroller supply, another 5 V low-dropout voltage regulator with off-board protection for e.g. sensor supply, a HS-CAN transceiver supporting CAN FD for data transmission, a high-voltage GPIO with embedded protective functions and a 16-bit Serial Peripheral Interface (SPI) to control and monitor the device. Also a configurable timeout / window watchdog circuit with a reset feature, one dedicated fail output and an undervoltage reset feature are implemented.

The device offers low-power modes in order to minimize current consumption in applications that are connected permanently to the battery. A wake-up from the low-power mode is possible via a message on the CAN bus, via the bi-level sensitive monitoring/wake-up input as well as via Cyclic Wake.

The device is designed to withstand the severe conditions of automotive applications

| Туре      | Package       | Marking   |

|-----------|---------------|-----------|

| TLE9471ES | PG-TSDSO-24-1 | TLE9471ES |

# **Table of Contents**

| 1           | Overview                                                   | . 1 |

|-------------|------------------------------------------------------------|-----|

| 2           | Block Diagram                                              | . 6 |

| 3           | Pin Configuration                                          | . 7 |

| 3.1         | Pin Assignment                                             |     |

| 3.2         | Pin Definitions and Functions                              | . 7 |

| 3.3         | Hints for Unused Pins                                      |     |

| 3.4         | Hints for Alternative Pin Functions                        |     |

| 4           | General Product Characteristics                            | 10  |

| 4.1         | Absolute Maximum Ratings                                   |     |

| 4.2         | Functional Range                                           |     |

| 4.3         | Thermal Resistance                                         |     |

| 4.4         | Current Consumption                                        |     |

| 5           | System Features                                            |     |

| <b>5</b> .1 | Block Description of State Machine                         |     |

| 5.1.1       | Device Configuration and SBC Init Mode                     |     |

| 5.1.1.1     | Device Configuration                                       |     |

| 5.1.1.2     | SBC Init Mode                                              |     |

| 5.1.2       | SBC Normal Mode                                            |     |

| 5.1.3       | SBC Stop Mode                                              |     |

| 5.1.4       | SBC Sleep Mode SBC Sleep Mode                              |     |

| 5.1.4       | SBC Restart Mode                                           |     |

| 5.1.5       |                                                            |     |

|             | SBC Fail-Safe Mode                                         |     |

| 5.1.7       | SBC Development Mode                                       |     |

| 5.1.8       |                                                            |     |

| 5.2         | Wake Features                                              |     |

| 5.2.1       | Cyclic Sense                                               |     |

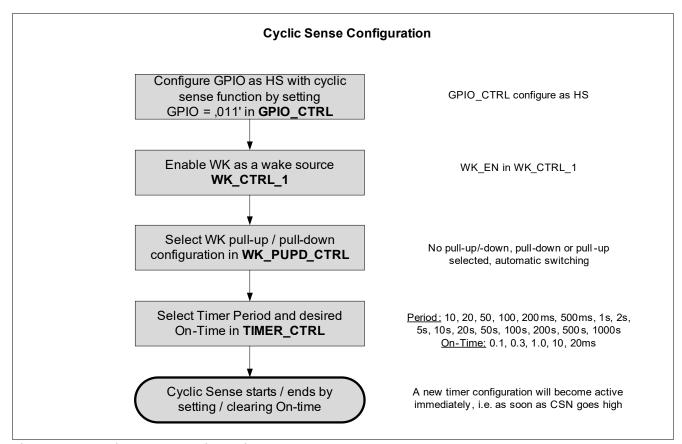

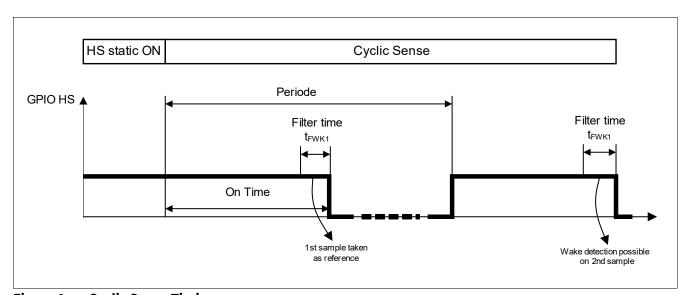

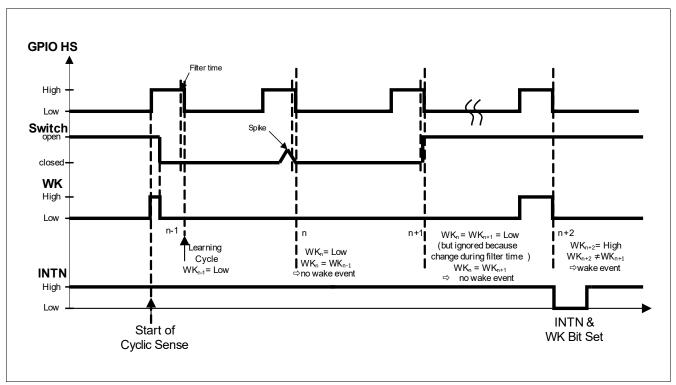

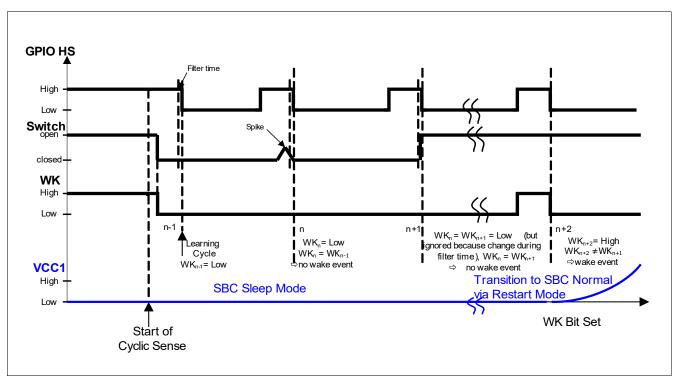

| 5.2.1.1     | Configuration and Operation of Cyclic Sense                |     |

| 5.2.1.2     | Cyclic Sense in Low-Power Mode                             |     |

| 5.2.2       | Cyclic Wake                                                |     |

| 5.2.3       | Internal Timer                                             |     |

| 5.3         | Charge Pump Output for Reverse Polarity Protection         |     |

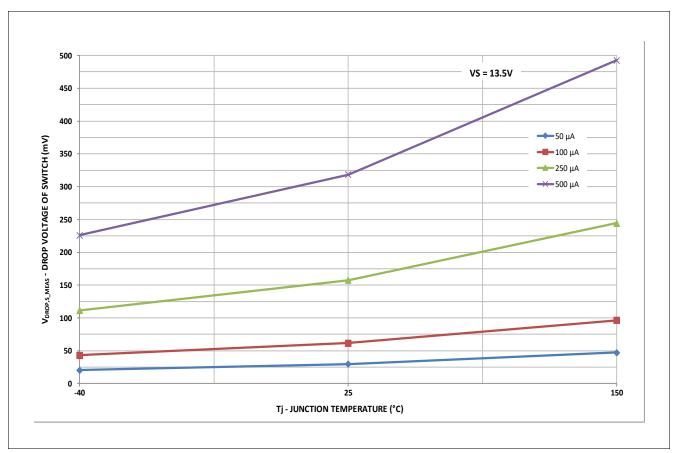

| 5.3.1       | Electrical Characteristics for Charge Pump                 |     |

| 5.4         | High-Voltage Measurement Interface                         |     |

| 5.4.1       | Block Description                                          |     |

| 5.4.2       | Functional Description                                     |     |

| 5.4.3       | Electrical Characteristics for Measurement Interface       |     |

| 5.5         | Spread Spectrum Modulation Frequency Function              | 43  |

| 6           | Voltage Regulator 1                                        |     |

| 6.1         | Block Description                                          |     |

| 6.2         | Functional Description                                     |     |

| 6.2.1       | Pulse With Modulation (PWM) and Spread Spectrum Modulation |     |

| 6.2.2       | Low-Power Mode Operation                                   |     |

| 6.2.3       | PWM to Low-Power Mode Handover                             |     |

| 6.2.4       | External Components Selection                              |     |

| 6.3         | Electrical Characteristics                                 | 47  |

| 1      | voltage Regulator 2                                        |      |

|--------|------------------------------------------------------------|------|

| 7.1    | Block Description                                          | 49   |

| 7.2    | Functional Description                                     | 50   |

| 7.2.1  | Short to Battery Protection                                | 50   |

| 7.3    | Electrical Characteristics                                 | 51   |

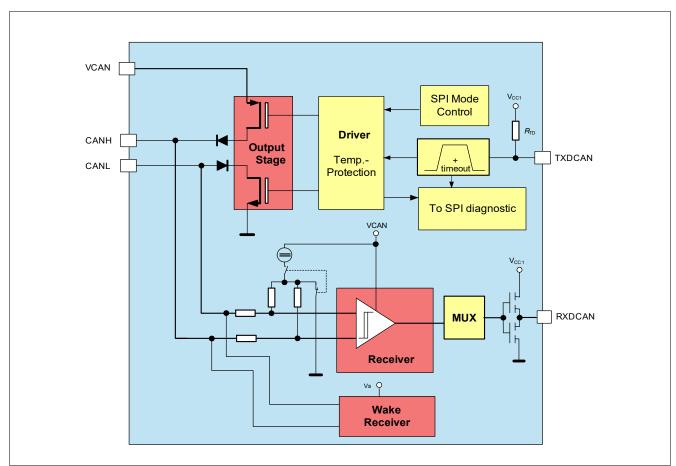

| 8      | High-Speed CAN FD Transceiver                              |      |

| 8.1    | Block Description                                          |      |

| 8.2    | Functional Description                                     | 54   |

| 8.2.1  | CAN Off Mode                                               | 56   |

| 8.2.2  | CAN Normal Mode                                            | 56   |

| 8.2.3  | CAN Receive Only Mode                                      | 57   |

| 8.2.4  | CAN Wake Capable Mode                                      | 57   |

| 8.2.5  | CAN Bus termination                                        | 58   |

| 8.2.6  | TXD Time-out Feature                                       | 58   |

| 8.2.7  | Bus Dominant Clamping                                      | 59   |

| 8.2.8  | Undervoltage Detection                                     | 59   |

| 8.3    | Electrical Characteristics                                 | 60   |

| 9      | High-Voltage Wake and Voltage Monitoring Input             | 67   |

| 9.1    | Block Description                                          | 67   |

| 9.2    | High-Voltage Wake Function                                 | 68   |

| 9.2.1  | Functional Description                                     | 68   |

| 9.2.2  | Wake Input Configuration                                   | 69   |

| 9.2.3  | Wake configuration for Cyclic Sense                        | 70   |

| 9.2.4  | High-Voltage Sensing as Alternate Function                 |      |

| 9.3    | Electrical Characteristics                                 |      |

| 10     | Interrupt Function                                         | 72   |

| 10.1   | Block and Functional Description                           |      |

| 10.2   | Electrical Characteristics                                 |      |

| 11     | Fail Output (FO) and General Purpose I/O (GPIO)            | 75   |

| 11.1   | Block and Functional Description                           |      |

| 11.1.1 | Fail-Output Function                                       | 76   |

| 11.1.2 | General Purpose I/O Function as Alternative Function       | . 77 |

| 11.1.3 | WK and FO/GPIO HV-Sensing Function as Alternative Function |      |

| 11.2   | Electrical Characteristics                                 |      |

| 12     | Supervision Functions                                      | 83   |

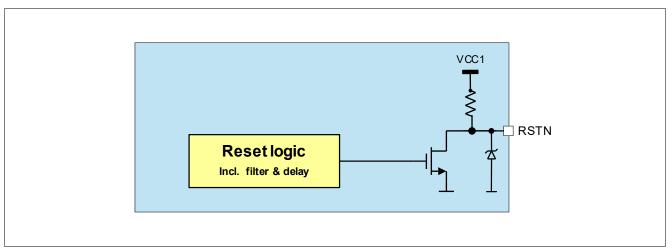

| 12.1   | Reset Function                                             | 83   |

| 12.1.1 | Reset Output Description                                   | 83   |

| 12.1.2 | Soft Reset Description                                     | 84   |

| 12.2   | Watchdog Function                                          |      |

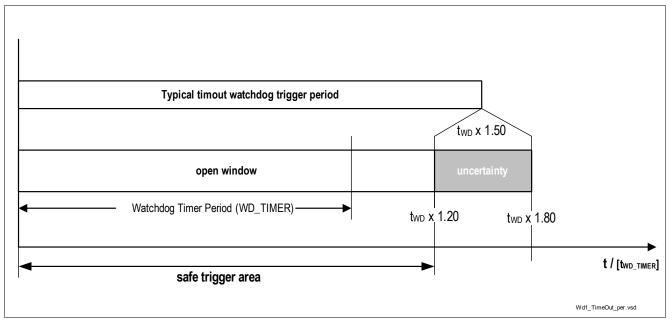

| 12.2.1 | Time-Out Watchdog                                          |      |

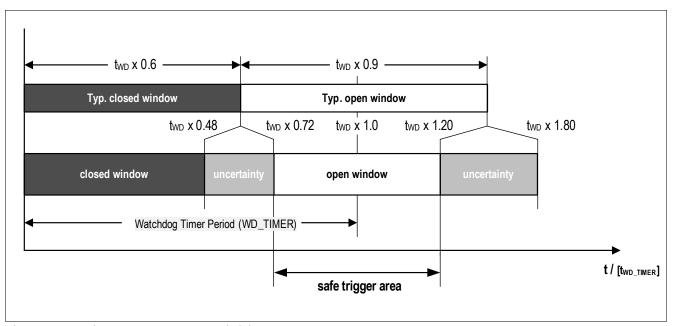

| 12.2.2 | Window Watchdog                                            |      |

| 12.2.3 | Watchdog Setting Check Sum                                 |      |

| 12.2.4 | Watchdog during SBC Stop Mode                              |      |

| 12.2.5 | Watchdog Start in SBC Stop Mode due to Bus Wake            |      |

| 12.3   | VS Power-On Reset                                          |      |

| 12.4   | VS Under- and Overvoltage                                  |      |

| '      |                                                            | 50   |

| 16     | Revision History                                     | . 141 |

|--------|------------------------------------------------------|-------|

| 15     | Package Outlines                                     | . 140 |

| 14.4   | Further Application Information                      | . 139 |

| 14.3   | Thermal Behavior of Package                          |       |

| 14.2   | ESD Tests                                            |       |

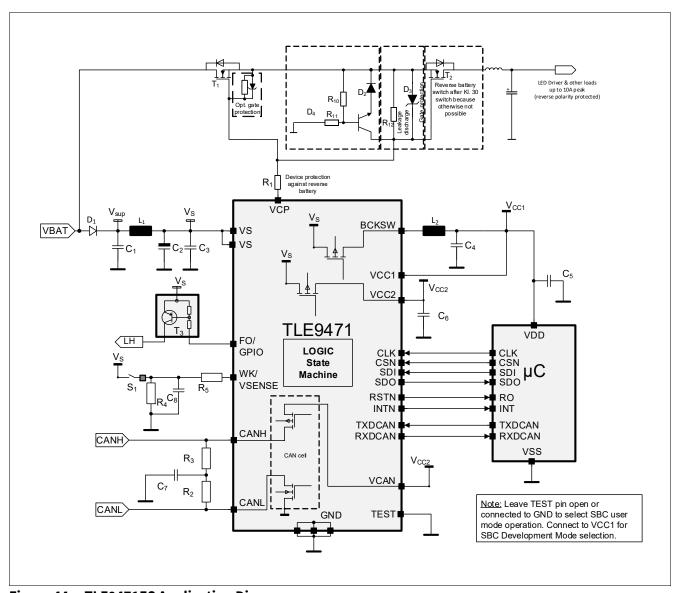

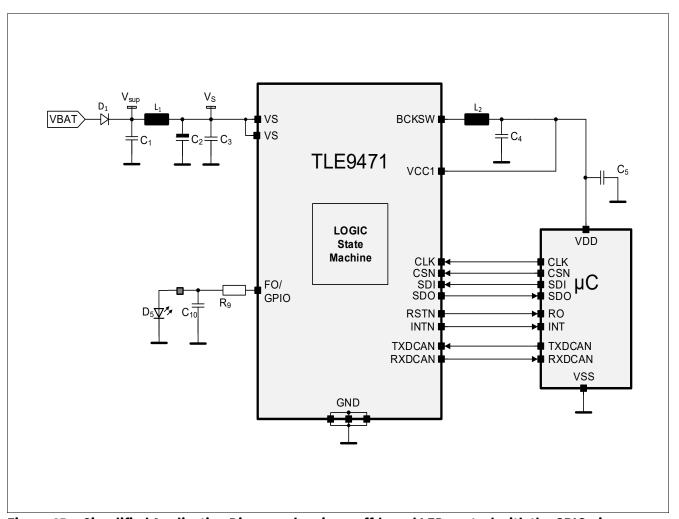

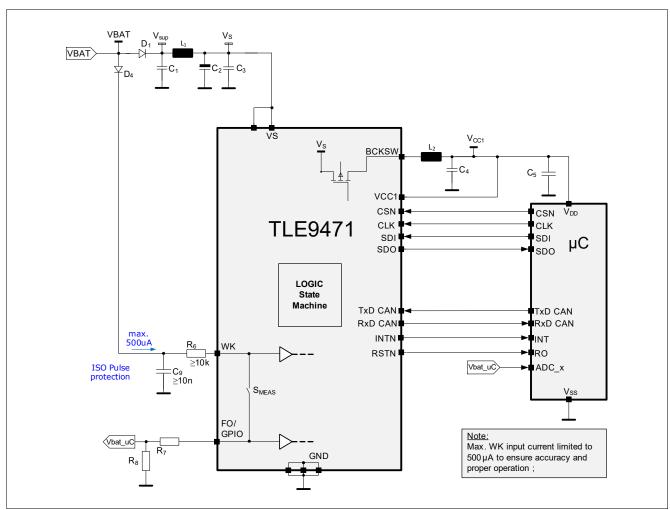

| 14.1   | Application Diagrams                                 |       |

| 14     | Application Information                              | . 131 |

| 13.7   | Electrical Characteristics                           | . 129 |

| 13.6.2 | Family and Product Information Register              |       |

| 13.6.1 | General Status Registers                             | . 121 |

| 13.6   | SPI Status Information Registers                     |       |

| 13.5.1 | General Control Registers                            |       |

| 13.5   | SPI Control Registers                                |       |

| 13.4   | SPI Bit Mapping                                      |       |

| 13.3   | SPI Programming                                      |       |

| 13.2   | Failure Signalization in the SPI Data Output         |       |

| 13.1   | SPI Block Description                                |       |

| 13     | Serial Peripheral Interface                          | 98    |

| 12.9   | Electrical Characteristics                           | 94    |

| 12.8.3 | SBC Thermal Shutdown                                 |       |

| 12.8.2 | Temperature Prewarning                               | 93    |

| 12.8.1 | Individual Thermal Shutdown                          | 93    |

| 12.8   | Thermal Protection                                   |       |

| 12.7   | VCC2 Undervoltage and VCAN Undervoltage              | 92    |

| 12.6   | VCC1 Short Circuit Diagnostics                       |       |

| 12.5.2 | VCC1 Overvoltage                                     |       |

| 12.5.1 | VCC1 Undervoltage and Undervoltage Prewarning        |       |

| 12.5   | VCC1 Over-/ Undervoltage and Undervoltage Prewarning |       |

| 12.4.2 | VS Overvoltage                                       |       |

| 12.4.1 | VS Undervoltage                                      | 90    |

# 2 Block Diagram

Figure 1 TLE9471ES Block Diagram

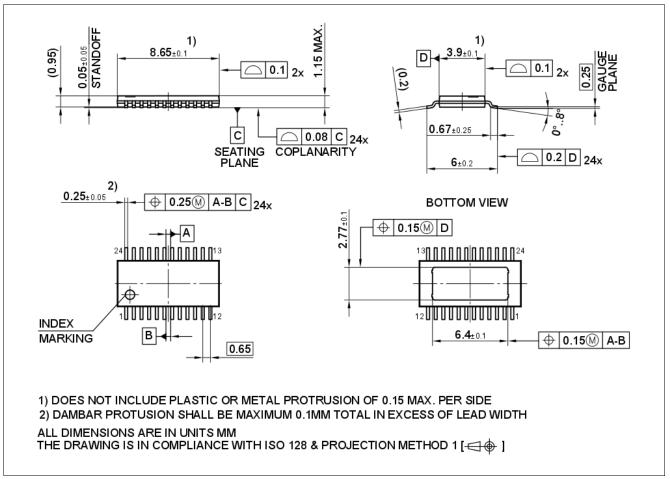

**Pin Configuration**

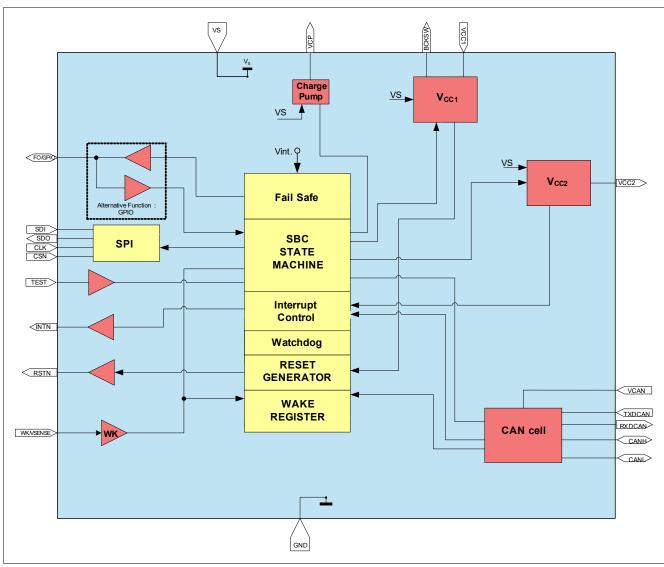

# **3** Pin Configuration

# 3.1 Pin Assignment

Figure 2 Pin Configuration

## 3.2 Pin Definitions and Functions

| Pin | Symbol | Function                                                                                                                                                                                                                                                                                                               |

|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | VCAN   | <b>HS-CAN Supply Input;</b> Supply needed for CAN Normal and Receive Only Mode                                                                                                                                                                                                                                         |

| 2   | TXDCAN | Transmit CAN                                                                                                                                                                                                                                                                                                           |

| 3   | RXDCAN | Receive CAN                                                                                                                                                                                                                                                                                                            |

| 4   | CLK    | SPI Clock Input                                                                                                                                                                                                                                                                                                        |

| 5   | SDI    | SPI Data Input; input for SBC (=MOSI)                                                                                                                                                                                                                                                                                  |

| 6   | SDO    | SPI Data Output; output from SBC (=MISO)                                                                                                                                                                                                                                                                               |

| 7   | CSN    | SPI Chip Select Input; active low                                                                                                                                                                                                                                                                                      |

| 8   | INTN   | <b>Interrupt Output;</b> used as wake-up flag for microcontroller in SBC Stop or Normal Mode and for indicating failures. Active low. During start-up used to set the SBC configuration in case of watchdog trigger failure. External pull-up (typ. 47 k $\Omega$ ) sets config 1/3, otherwise config 2/4 is selected. |

### **Pin Configuration**

| r leave open for normal user mode operation; ower-on to activate SBC Development Mode ited pull-down resistor.  Feedback Input for Buck Converter er Supply Output ot bonded  VCC1 power stage - both VS pins must be connected |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| rower-on to activate SBC Development Mode ated pull-down resistor.  Feedback Input for Buck Converter  For Supply Output  ot bonded  VCC1 power stage - both VS pins must be connected                                          |

| ot bonded  VCC1 power stage - both VS pins must be connected                                                                                                                                                                    |

| ot bonded  VCC1 power stage - both VS pins must be connected                                                                                                                                                                    |

| ot bonded<br>VCC1 power stage - both VS pins must be connected                                                                                                                                                                  |

| VCC1 power stage - both VS pins must be connected                                                                                                                                                                               |

| •                                                                                                                                                                                                                               |

| otential for proper operation; Connect to battery protection diode and filter against EMC                                                                                                                                       |

| ly of device - both VS pins must be connected otential for proper operation; Connect to battery protection diode and filter against EMC                                                                                         |

| driving the gate of external N-channel MOSFETs, e.g. on or Kl.30 load switch. Always place a $1k\Omega$ resistor                                                                                                                |

| nction: HV-measurement function input                                                                                                                                                                                           |

| tput, active low;<br>configurable pin as WK, LS-, or HS-witch supplied by<br>hapter 11.1.1)<br>function: if HV-measurement function is configured                                                                               |

| t                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                 |

| ad; For cooling purposes only, connect to but do not                                                                                                                                                                            |

|                                                                                                                                                                                                                                 |

<sup>1)</sup> The exposed die pad at the bottom of the package allows better power dissipation of heat from the SBC via the PCB. The exposed die pad is not connected to any active part of the IC. However, it should be connected to GND for the best EMC performance.

Note: Both VS Pins must be connected to same battery potential; all GND pins as well as the Cooling Tab must be connected to one common GND potential

# infineon

## **Pin Configuration**

### 3.3 Hints for Unused Pins

In case functions or pins are not used, it must be ensured that the configurations are done properly, e.g. disabled via SPI. Unused pins should be handled as follows:

- WK/VSENSE: connect to GND and disable WK inputs via SPI

- RSTN / INTN / FO: leave open

- VCC2 / VCP: leave open and keep disabled

- VCAN: connect to VCC1

- CANH/L, RXDCAN, TXDCAN: leave all pins open

- TEST: Leave open or connect to GND for normal user mode operation or connect to VCC1 to activate SBC Development Mode;

- **n.c.**: not connected; internally not bonded; leave open

- If unused pins are routed to an external connector which leaves the ECU, then these pins should have provision for a jumper (depopulated if unused)

### 3.4 Hints for Alternative Pin Functions

In case of SPI selectable alternative pin functions, it must be ensured that the correct configurations are also selected via SPI (in case it is not done automatically). Please consult the respective chapter. In addition, following topics shall be considered:

- WK/VSENSE: The pin can be either used as high-voltage wake-up and monitoring function or for a voltage measurement function (via bit setting WK\_MEAS = '1'). In the second case, the WK pin shall not be used / assigned for any wake-up detection nor Cyclic Sense functionality, i.e. WK must be disabled in the register WK\_CTRL\_1 and the level information must be ignored in the register WK\_LVL\_STAT.

- FO/GPIO: The pin can also be configured as a GPIO in the GPIO\_CTRL register. In this case, the pin shall not be used for any fail output functionality.

The default configuration after start-up or power on reset (POR) is FO.

## **General Product Characteristics**

# **4** General Product Characteristics

# 4.1 Absolute Maximum Ratings

# Table 1 Absolute Maximum Ratings<sup>1)</sup>

$T_{\rm j}$  = -40°C to +150°C; all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                         | Symbol                     | Values |      |                            | Unit | Note or                                                   | Number   |

|---------------------------------------------------|----------------------------|--------|------|----------------------------|------|-----------------------------------------------------------|----------|

|                                                   |                            | Min.   | Тур. | Max.                       |      | <b>Test Condition</b>                                     |          |

| Voltages                                          |                            |        |      |                            |      |                                                           |          |

| Supply Voltage VS                                 | V <sub>S, max</sub>        | -0.3   | -    | 28                         | V    | _                                                         | P_4.1.1  |

| Supply Voltage VS                                 | V <sub>S, max</sub>        | -0.3   | -    | 40                         | V    | Load Dump,<br>max. 400 ms                                 | P_4.1.2  |

| Voltage Regulator 1 Sense<br>Input                | V <sub>CC1, max</sub>      | -0.3   | -    | 5.5                        | V    | 2)                                                        | P_4.1.3  |

| Buck Switch Pin BCKSW                             | V <sub>BCKSW, max</sub>    | -0.3   | -    | V <sub>S</sub> + 0.3       | V    | _                                                         | P_4.1.4  |

| Voltage Regulator 2 Output                        | V <sub>CC2, max</sub>      | -0.3   | -    | 28                         | V    | V <sub>CC2</sub> = 40 V for<br>Load Dump,<br>max. 400 ms; | P_4.1.5  |

| Charge Pump Output                                | V <sub>CP, max</sub>       | -0.3   | -    | <i>V</i> <sub>S</sub> + 16 | V    |                                                           | P_4.1.6  |

| Wake Input WK/VSENSE                              | V <sub>WK, max</sub>       | -0.3   | -    | 40                         | V    | _                                                         | P_4.1.7  |

| Fail Output FO/GPIO                               | V <sub>FO_TEST, max</sub>  | -0.3   | -    | V <sub>S</sub> + 0.3       | V    | _                                                         | P_4.1.8  |

| CANH, CANL                                        | V <sub>BUS, max</sub>      | -27    | -    | 40                         | V    | -                                                         | P_4.1.9  |

| Logic Input Pins (CSN, CLK,<br>SDI, TXDCAN, TEST) | V <sub>I, max</sub>        | -0.3   | -    | V <sub>CC1</sub> + 0.3     | V    | _                                                         | P_4.1.10 |

| Logic Output Pins (SDO,<br>RSTN, INTN, RXDCAN)    | V <sub>O, max</sub>        | -0.3   | -    | V <sub>CC1</sub> + 0.3     | V    | _                                                         | P_4.1.11 |

| VCAN Input Voltage                                | $V_{\rm VCAN,max}$         | -0.3   | _    | 5.5                        | V    | -                                                         | P_4.1.12 |

| Maximum Differential CAN<br>Bus Voltage           | V <sub>CAN_Diff, max</sub> | -5     | -    | 10                         | V    | _                                                         | P_4.1.20 |

| Temperatures                                      |                            |        |      |                            |      |                                                           |          |

| Junction Temperature                              | $T_{\rm j}$                | -40    | -    | 150                        | °C   | _                                                         | P_4.1.13 |

| Storage Temperature                               | $T_{\rm stg}$              | -55    | -    | 150                        | °C   | _                                                         | P_4.1.14 |

| ESD Susceptibility                                |                            |        |      |                            |      |                                                           |          |

| ESD Resistivity                                   | $V_{\rm ESD,11}$           | -2     | -    | 2                          | kV   | HBM <sup>3)</sup>                                         | P_4.1.15 |

| ESD Resistivity to GND,<br>CANH, CANL             | V <sub>ESD,12</sub>        | -8     | -    | 8                          | kV   | HBM <sup>4)3)</sup>                                       | P_4.1.16 |

# TLE9471ES

# **Lite CAN SBC Family**

#### **General Product Characteristics**

## Table 1 Absolute Maximum Ratings<sup>1)</sup> (cont'd)

$T_{\rm j}$  = -40°C to +150°C; all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                                  | Symbol              | Values |      |      | Unit | Note or               | Number   |

|------------------------------------------------------------|---------------------|--------|------|------|------|-----------------------|----------|

|                                                            |                     | Min.   | Тур. | Max. |      | <b>Test Condition</b> |          |

| ESD Resistivity to GND                                     | $V_{\rm ESD,21}$    | -500   | _    | 500  | V    | CDM <sup>5)</sup>     | P_4.1.17 |

| ESD Resistivity Pin 1,<br>12,13,24 (corner pins) to<br>GND | V <sub>ESD,22</sub> | -750   | -    | 750  | V    | CDM <sup>5)</sup>     | P_4.1.18 |

- 1) Not subject to production test, specified by design.

- 2) The VCC1 and digital I/O maximum rating can be 6.0 V for a limited time (up to 100h).

- 3) ESD susceptibility, HBM according to ANSI/ESDA/JEDEC JS-001 (1.5 k $\Omega$ , 100 pF)

- 4) Please see chapter "Application Information" For ESD "GUN" resistivity (according to IEC61000-4-2 "gun test" (150 pF,  $330 \Omega$ )).

- 5) ESD susceptibility, Charged Device Model "CDM" EIA/JESD22-C101 or ESDA STM5.3.1

### **Notes**

- 1. Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- 2. Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

## **Lite CAN SBC Family**

#### **General Product Characteristics**

#### 4.2 **Functional Range**

Functional Range<sup>1)</sup> Table 2

| Parameter            | Symbol             |           | Value | s    | Unit | Note or<br>Test Condition                                         | Number  |

|----------------------|--------------------|-----------|-------|------|------|-------------------------------------------------------------------|---------|

|                      |                    | Min.      | Тур.  | Max. |      |                                                                   |         |

| Supply Voltage       | $V_{\rm S,func}$   | $V_{POR}$ | -     | 28   | V    | <sup>2)</sup> V <sub>POR</sub> see section<br><b>Chapter 12.9</b> | P_4.2.1 |

| CAN Supply Voltage   | $V_{\rm CAN,func}$ | 4.75      | _     | 5.25 | ٧    | _                                                                 | P_4.2.2 |

| SPI Frequency        | f <sub>SPI</sub>   | -         | -     | 4    | MHz  | see Chapter 13.7 for f <sub>SPI,max</sub>                         | P_4.2.3 |

| Junction Temperature | T <sub>j</sub>     | -40       | _     | 150  | °C   | -                                                                 | P_4.2.4 |

<sup>1)</sup> Not subject to production test, specified by design.

Note:

Within the functional range the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the related electrical characteristics table.

### **Device Behavior Outside of Specified Functional Range:**

- 28V <  $V_{S,func}$  < 40V: Device is still functional (including the state machine); the specified electrical characteristics might not be ensured anymore. The regulators VCC1/2 are working properly, however, a thermal shutdown might occur due to high power dissipation. The specified SPI communication speed is ensured; the absolute maximum ratings are not violated, however the device is not intended for continuous operation of VS >28V. The device operation at high junction temperatures for long periods might reduce the operating life time;

- $V_{\text{CAN}}$  < 4.75V: The undervoltage bit **VCAN\_UV** is set in the SPI register **BUS\_STAT** and the transmitter is disabled as long as the UV condition is present;

- $5.25V < V_{CAN} < 6.0V$ : CAN transceiver is still functional. However, the communication might fail due to outof-spec operation;

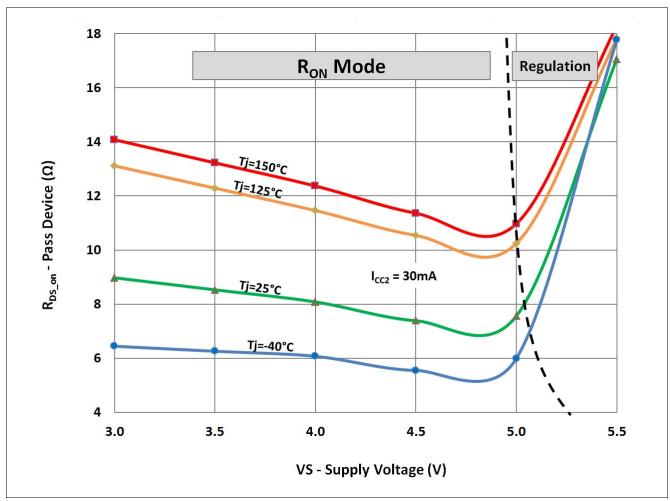

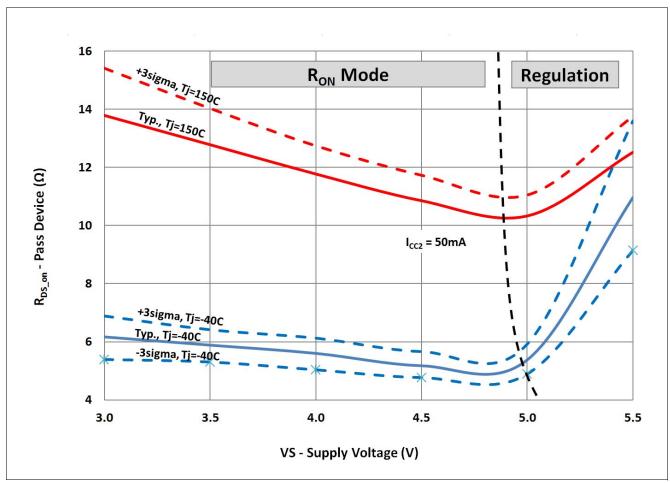

- V<sub>POR.f</sub> < VS < 5.5V: Device is still functional; the specified electrical characteristics might not be ensured anymore:

- The voltage regulators will enter the linear (R<sub>DS, On</sub>) operation mode,

- A VCC1\_UV reset could be triggered depending on the Vrtx settings,

- GPIO behavior depends on the respective configuration:

- HS/LS switches remain switched On as long as the control voltage is sufficient.

- An unwanted overcurrent shutdown may occur.

- OC shutdown bit set and the respective HS/LS switch will turn Off;

- FO output remains On if it was enabled before VS > 5.5V,

- The specified SPI communication speed is ensured.

<sup>2)</sup> Including Power-On Reset, Over- and Undervoltage Protection

### **General Product Characteristics**

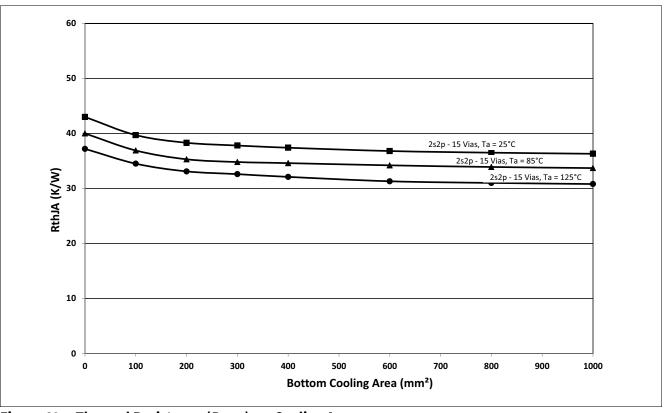

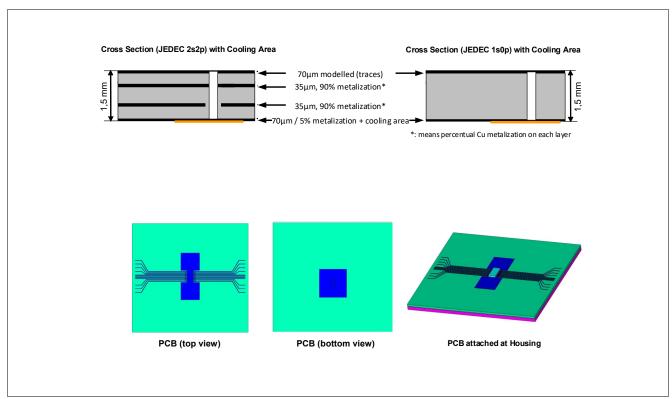

#### **Thermal Resistance** 4.3

#### Thermal Resistance<sup>1)</sup> Table 3

| Parameter                   | Symbol        | Values |      | Unit | Note or | Number         |         |

|-----------------------------|---------------|--------|------|------|---------|----------------|---------|

|                             |               | Min.   | Тур. | Max. |         | Test Condition |         |

| Junction to Soldering Point | $R_{th(JSP)}$ | -      | 14   | _    | K/W     | Exposed Pad    | P_4.3.1 |

| Junction to Ambient         | $R_{th(JA)}$  | -      | 35   | _    | K/W     | 2)             | P_4.3.2 |

<sup>1)</sup> Not subject to production test, specified by design.

<sup>2)</sup> Specified  $R_{th(JA)}$  value is according to Jedec JESD51-2,-5,-7 at natural convection on FR4 2s2p board for a power dissipation of 1.5W; the product (chip+package) was simulated on a 76.2x114.3x1.5mm³ with 2 inner copper layers (2 x 70μm Cu, 2 x 35μm C); where applicable a thermal via array under the exposed pad contacted the first inner copper layer and 300mm2 cooling areas on the top layer and bottom layers (70μm).

### **General Product Characteristics**

#### **Current Consumption** 4.4

#### **Current Consumption** Table 4

Current consumption values are specified at  $T_i = 25$ °C,  $V_S = 13.5$  V, all outputs open (unless otherwise specified)

| Parameter                                                  | Symbol                 | Values |      |             | Unit | Note or                                                                                                                                 | Number  |

|------------------------------------------------------------|------------------------|--------|------|-------------|------|-----------------------------------------------------------------------------------------------------------------------------------------|---------|

|                                                            |                        | Min.   | Тур. | Max.        |      | <b>Test Condition</b>                                                                                                                   |         |

| SBC Normal Mode                                            | •                      |        | *    | <del></del> | *    |                                                                                                                                         | *       |

| Normal Mode current consumption                            | I <sub>Normal</sub>    | _      | 3.5  | 6.5         | mA   | $V_{\rm S}$ = 5.5 V to 28 V;<br>$T_{\rm j}$ = -40 °C to +150 °C;<br>VCC2, CAN = Off                                                     | P_4.4.1 |

| SBC Stop Mode                                              |                        |        |      |             |      |                                                                                                                                         |         |

| Stop Mode current consumption                              | I <sub>Stop_1,25</sub> | -      | 44   | 55          | μА   | 1) VCC2 & CAN = Off,<br>Cyclic Wake/Sense &<br>Watchdog = Off;<br>no load on VCC1;<br>I_PEAK_TH = '0'                                   | P_4.4.2 |

| Stop Mode current consumption                              | I <sub>Stop_1,85</sub> | -      | 50   | 72          | μΑ   | 1)2) $T_j = 85^{\circ}\text{C}$ ;<br>VCC2 & CAN = Off;<br>Cyclic Wake/Sense &<br>Watchdog = Off;<br>no load on VCC1;<br>I_PEAK_TH = '0' | P_4.4.3 |

| Stop Mode current consumption (high active peak threshold) | I <sub>Stop_2,25</sub> | -      | 65   | 72          | μА   | 1) VCC2 & CAN Cyclic<br>Wake/Sense &<br>Watchdog = Off;<br>no load on VCC1;<br>I_PEAK_TH = '1'                                          | P_4.4.4 |

| Stop Mode current consumption (high active peak threshold) | I <sub>Stop_2,85</sub> | -      | 70   | 92          | μА   | 1)2) $T_j = 85^{\circ}\text{C}$ ;<br>VCC2 & CAN<br>Cyclic Wake/Sense &<br>Watchdog = Off;<br>no load on VCC1;<br>I_PEAK_TH = '1'        | P_4.4.5 |

| SBC Sleep Mode                                             |                        |        |      |             |      |                                                                                                                                         |         |

| Sleep Mode current consumption                             | I <sub>Sleep,25</sub>  | _      | 15   | 25          | μΑ   | VCC2 & CAN= Off;<br>Cyclic Wake/Sense =<br>Off                                                                                          | P_4.4.6 |

| Sleep Mode current consumption                             | I <sub>Sleep,85</sub>  | -      | 25   | 35          | μΑ   | <sup>2)</sup> T <sub>j</sub> = 85°C;<br>VCC2 & CAN = Off;<br>Cyclic Wake/Sense =<br>Off                                                 | P_4.4.7 |

### **General Product Characteristics**

#### Table 4 **Current Consumption** (cont'd)

Current consumption values are specified at  $T_i = 25$  °C,  $V_S = 13.5$  V, all outputs open (unless otherwise specified)

| Parameter                                                          | Symbol                     | Values |      |      | Unit |                                                                                                                                      | Number   |

|--------------------------------------------------------------------|----------------------------|--------|------|------|------|--------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                                                    |                            | Min.   | Тур. | Max. |      | Test Condition                                                                                                                       |          |

| Feature Incremental Currer                                         | nt Consump                 | tion   | ,    |      |      |                                                                                                                                      | 1        |

| Current consumption for CAN module, recessive state                | I <sub>CAN,rec</sub>       | _      | 2    | 3    | mA   | <sup>2)</sup> SBC Normal/Stop<br>Mode; CAN Normal<br>Mode; VCC2<br>connected to VCAN;<br>VTXDCAN = VCC2; no<br>RL on CAN             | P_4.4.8  |

| Current consumption for CAN module, dominant state                 | I <sub>CAN,dom</sub>       | -      | 3    | 5    | mA   | <sup>2)</sup> SBC Normal/Stop<br>Mode; CAN Normal<br>Mode; VCC1<br>connected to VCAN;<br>VTXDCAN = GND;<br>no RL on CAN              | P_4.4.9  |

| Current consumption for<br>CAN module, Receive Only<br>Mode        | I <sub>CAN,RcvOnly</sub>   | -      | 0.9  | 1.2  | mA   | <sup>2)</sup> SBC Normal/Stop<br>Mode; CAN Receive<br>Only Mode; VCC1<br>connected to VCAN;<br>VTXDCAN = VCC1; no<br>RL on CAN       | P_4.4.10 |

| Current consumption for WK, GPIO wake capability (all wake inputs) | I <sub>Wake,WK,25</sub>    | -      | 0.2  | 2    | μА   | 3)4)5) SBC Sleep Mode;<br>WK wake capable;<br>no activity on WK pin;<br>CAN = Off; VCC2 = Off                                        | P_4.4.13 |

| Current consumption for WK, GPIO wake capability (all wake inputs) | I <sub>Wake,WK,85</sub>    | _      | 0.5  | 3    | μΑ   | $^{2)3)4)5)}$ SBC Sleep Mode;<br>$T_j = 85^{\circ}\text{C}$ ;<br>WK wake capable;<br>no activity on WK pin;<br>CAN = Off; VCC2 = Off | P_4.4.14 |

| Current consumption for CAN wake capability                        | I <sub>Wake,CAN,25</sub>   | _      | 4.5  | 6    | μА   | <sup>3)</sup> SBC Sleep Mode;<br>CAN Wake Capable;<br>WK = Off; VCC2 = Off;                                                          | P_4.4.15 |

| Current consumption for CAN wake capability                        | I <sub>Wake,CAN,85</sub>   | -      | 5.5  | 7    | μА   | <sup>2)3)</sup> SBC Sleep Mode; $T_j$<br>= 85°C;<br>CAN Wake Capable;<br>WK = Off; VCC2 = Off;                                       | P_4.4.16 |

| VCC2 Normal Mode current consumption                               | I <sub>Normal,VCC2</sub>   | _      | 2.5  | 3.5  | mA   | $V_{\rm S}$ = 5.5 V to 28 V;<br>$T_{\rm j}$ = -40 °C to +150 °C;<br>VCC2 = On (no load)                                              | P_4.4.17 |

| Current consumption for VCC2 in SBC Sleep Mode                     | I <sub>Sleep,VCC2,25</sub> | _      | 25   | 35   | μΑ   | <sup>1)3)</sup> SBC Sleep Mode;<br>VCC2 = On (no load);<br>CAN, WK = Off                                                             | P_4.4.18 |

#### **General Product Characteristics**

### **Table 4** Current Consumption (cont'd)

Current consumption values are specified at  $T_i = 25$ °C,  $V_S = 13.5$  V, all outputs open (unless otherwise specified)

| Parameter                                                                                     | Symbol                     | Values    |     |      | Unit | Note or                                                                                                                         | Number   |  |

|-----------------------------------------------------------------------------------------------|----------------------------|-----------|-----|------|------|---------------------------------------------------------------------------------------------------------------------------------|----------|--|

|                                                                                               |                            | Min. Typ. |     | Max. |      | Test Condition                                                                                                                  |          |  |

| Current consumption for VCC2 in SBC Sleep Mode                                                | I <sub>Sleep,VCC2,85</sub> | -         | 30  | 40   | μΑ   | $T_j = 85^{\circ}\text{C}$ ; VCC2 = On (no load); CAN, WK = Off                                                                 | P_4.4.19 |  |

| Current consumption for<br>GPIO if configured as low-<br>side / high-side in SBC Stop<br>Mode | I <sub>Stop,GPIO,25</sub>  | _         | 400 | 550  | μΑ   | <sup>2)3)</sup> SBC Stop Mode;<br>GPIO configured as HS<br>or LS with 100% duty<br>cycle (no load);<br>CAN, WK = Off            | P_4.4.20 |  |

| Current consumption for<br>GPIO if configured as low-<br>side / high-side in SBC Stop<br>Mode | I <sub>Stop,GPIO,85</sub>  | -         | 450 | 600  | μΑ   | $^{2)3)}$ SBC Stop Mode;<br>$T_j$ = 85°C;<br>GPIO configured as HS<br>or LS with 100% duty<br>cycle (no load);<br>CAN, WK = Off | P_4.4.21 |  |

| Current consumption for Cyclic Sense function                                                 | I <sub>Stop,CS25</sub>     | -         | 20  | 26   | μΑ   | <sup>3)6)7)</sup> SBC Stop Mode;<br>WD = Off;                                                                                   | P_4.4.22 |  |

| Current consumption for Cyclic Sense function                                                 | I <sub>Stop,CS85</sub>     | _         | 24  | 35   | μΑ   | $^{2)3)6)7)}$ SBC Stop Mode;<br>$T_{j} = 85^{\circ}C;$<br>WD = Off;                                                             | P_4.4.23 |  |

| Current consumption for watchdog active in Stop Mode                                          | I <sub>Stop,WD25</sub>     | -         | 20  | 26   | μΑ   | <sup>2)</sup> SBC Stop Mode;<br>Watchdog running;                                                                               | P_4.4.24 |  |

| Current consumption for watchdog active in Stop Mode                                          | I <sub>Stop,WD85</sub>     | _         | 24  | 35   | μΑ   | <sup>2)</sup> SBC Stop Mode;<br>$T_j = 85^{\circ}\text{C}$ ;<br>Watchdog running;                                               | P_4.4.25 |  |

<sup>1)</sup> If the load current on VCC1 exceeds the configured VCC1 active peak threshold I<sub>BCKSW,Ipeak1,r</sub> or I<sub>BCKSW,Ipeak2,r</sub>, the current consumption will increase by typ. 2.9mA to ensure optimum dynamic load behavior. Same applies to VCC2. See also Chapter 6, Chapter 7.

<sup>2)</sup> Not subject to production test, specified by design.

<sup>3)</sup> Current consumption adders of the features defined for SBC Stop Mode also apply for SBC Sleep Mode and vice versa. The wake input signals are stable (i.e. not toggling), Cyclic Wake/Sense & watchdog are Off (unless otherwise specified).

<sup>4)</sup> No pull-up or pull-down configuration selected.

<sup>5)</sup> The specified WK current consumption adder for wake capability applies regardless of how many WK inputs are activated, i.e GPIO configured as wake input.

### **General Product Characteristics**

6) GPIO configured as HS used for Cyclic Sense, Timer with 20ms period, 0.1ms on-time, no load on GPIO.

In general the current consumption adder for Cyclic Sense in SBC Stop Mode can be calculated with below equation (no load on FO/GPIO):

IStop,CS\_typ =  $18\mu$ A + ( $I_{Stop,GPIO,25}$  × ton/TPer)

where 18uA is the base current consumption of the digital Cyclic Sense / wake-up functionality;

7) Also applies to Cyclic Wake but without the contribution of the HS biasing

### **Notes**

- 1. There is no additional current consumption in SBC Normal Mode due to PWM generators or Timers.

- 2. To ensure the device functionality down to  $V_{por,f}$  the quiescent current will increase gradually by ~35 uA for  $V_S$  < 9 V in SBC Stop Mode and Sleep Mode..

# infineon

### **System Features**

# 5 System Features

This chapter describes the system features and behavior of the TLE9471ES:

- State machine

- Device configuration

- SBC mode control

- State of supplies and peripherals

- · System functions such as Cyclic Sense or Cyclic Wake

- Charge pump output for reverse polarity protection and Kl. 30 load switching

- High-voltage measurement interface

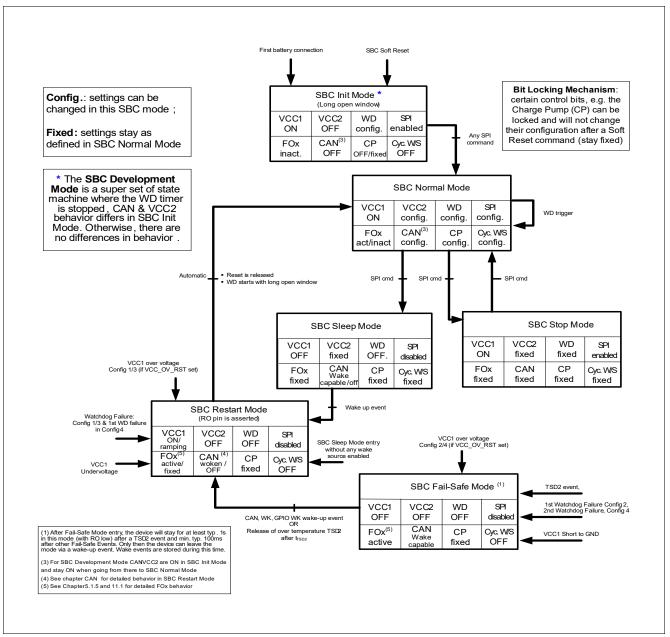

The System Basis Chip (SBC) offers six operating modes:

- SBC Init Mode: Power-up of the device (initial and after a soft reset),

- SBC Normal Mode: The main operating mode of the device,

- SBC Stop Mode: The first-level power saving mode (the main voltage regulator VCC1 remains enabled),

- SBC Sleep Mode: The second-level power saving mode (VCC1 is disabled),

- SBC Restart Mode: An intermediate mode after a wake-up event from SBC Sleep or Fail-Safe Mode or after

a failure (e.g. WD failure, VCC1 under voltage reset) to bring the microcontroller into a defined state via a

reset. Once the failure condition is not present anymore the device will automatically change to SBC

Normal Mode after a delay time (t<sub>RD1</sub> or t<sub>RD2</sub>).

- SBC Fail-Safe Mode: A safe-state mode after critical failures (e.g. WD failure, VCC1 under voltage reset) to bring the system into a safe state and to ensure a proper restart of the system later on. VCC1 is disabled. It is a permanent state until either a wake-up event (via CAN, WK/VSENSE or GPIO configured as wake-up) occurs or the over temperature condition is not present anymore.

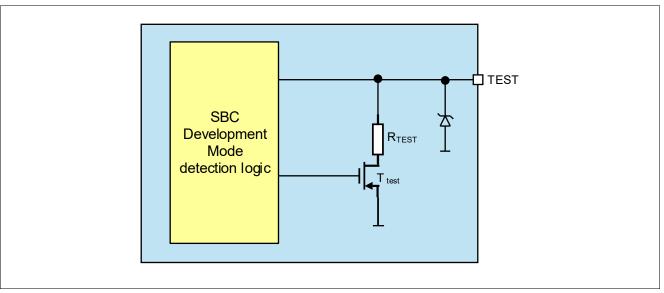

A special mode, called SBC Development Mode, is available during software development or debugging of the system. All above mentioned operating modes can be accessed in this mode. However, the watchdog counter is stopped and does not need to be triggered. In addition, CAN is set to normal mode and VCC2 is On. This mode can be accessed by connecting the TEST pin to VCC1 during SBC Init Mode.

The device can be configured via hardware to determine the device behavior after a watchdog trigger failure. See **Chapter 5.1.1** for further information.

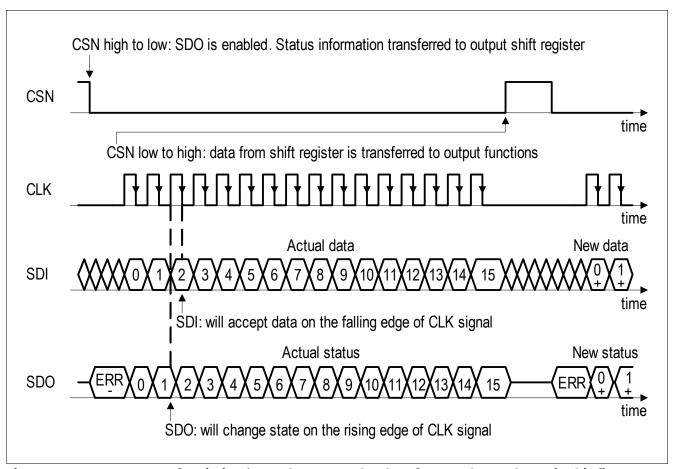

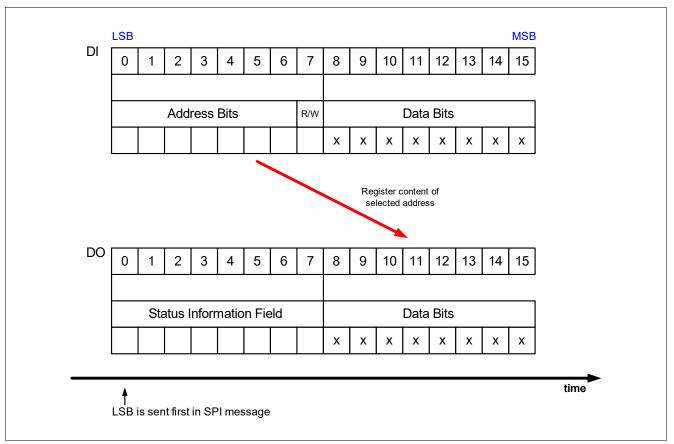

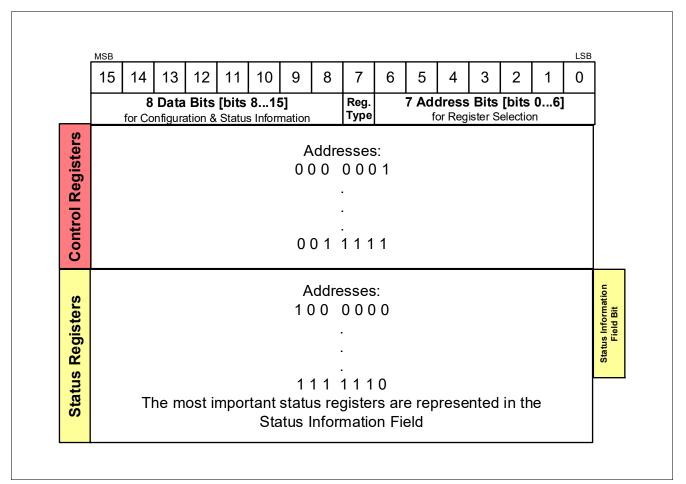

The System Basis Chip is controlled via a 16-bit SPI interface. A detailed description can be found in **Chapter 13**. The device configuration as well as the diagnosis is handled via the SPI. The SPI mapping of the TLE9471ES is compatible to other devices of the TLE926x and TLE927x families.

The device offers various supervision features to support functional safety requirements. Please see **Chapter 12** for more information.

# infineon

### **System Features**

## 5.1 Block Description of State Machine

The different SBC operating modes are selected via SPI by setting the respective SBC MODE bits in the register M\_S\_CTRL. The SBC MODE bits are cleared when going through SBC Restart Mode and thus always show the current SBC mode.

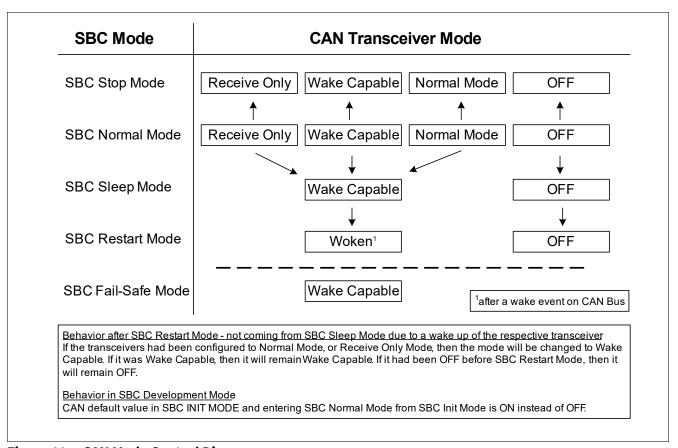

Figure 3 State Diagram showing the SBC Operating Modes

**System Features**

## 5.1.1 Device Configuration and SBC Init Mode

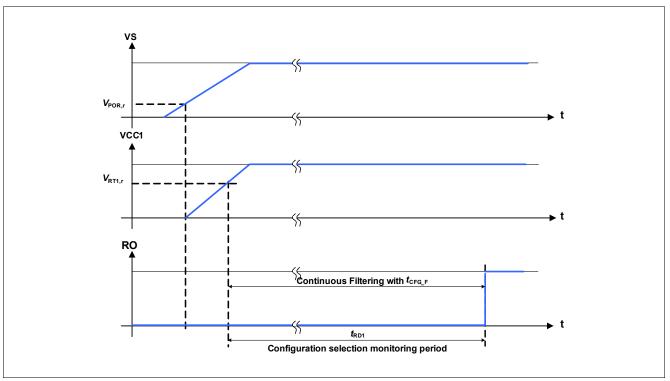

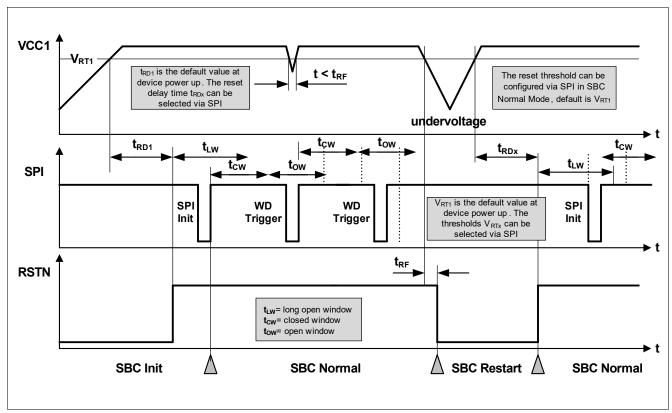

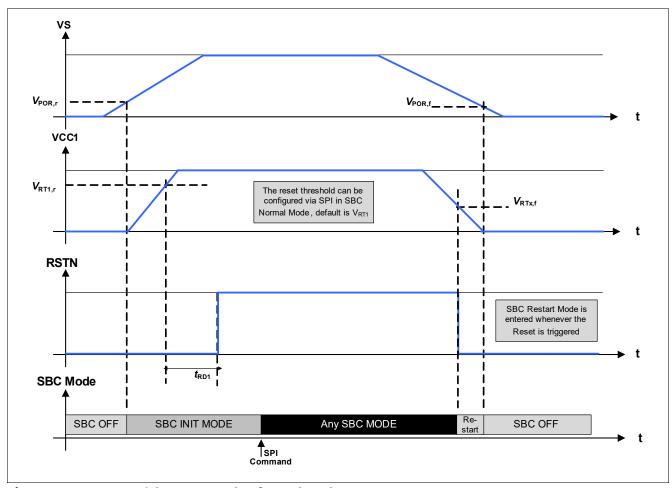

The device starts up in SBC Init Mode after crossing the power-on reset threshold  $V_{POR,r}$  (see also Chapter 12.3) and the watchdog starts with a long open window ( $t_{LW}$ ) after RSTN is released (High level). During this power-on phase the following configurations are stored in the device:

- The device behavior regarding a watchdog trigger failure and a VCC1 over voltage condition is determined by the external circuit on the INTN pin (typ. 47 k $\Omega$  pull-up resistor to VCC1, see also below)

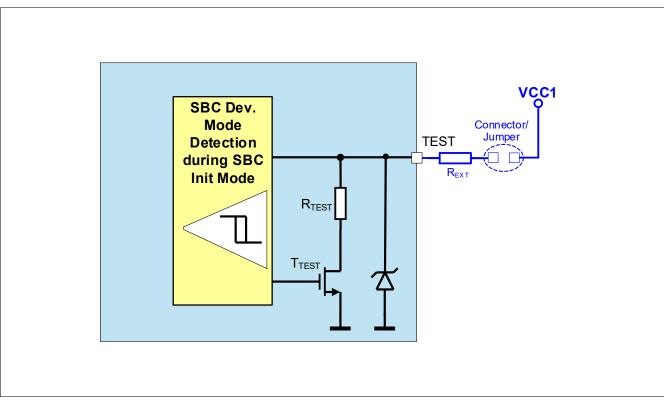

- The selection of the normal user mode operation or the SBC Development Mode (watchdog = Off, CAN = On, VCC2 = On for debugging purposes) is set depending on the voltage level of the TEST pin (see also Chapter 5.1.7).

## **5.1.1.1** Device Configuration

The configuration selects the SBC behavior due to a watchdog trigger failure and VCC1 overvoltage detection. Depending on the requirements of the application, two different configurations can be chosen:

- If the VCC1 output shall be switched Off and the device shall go to SBC Fail-Safe Mode in case of a watchdog failure (1 or 2 fails). To set this configuration (Config 2/4), the INTN pin does not need an external pull-up resistor.

- If VCC1 should not be switched Off (Config 1/3), the INTN pin needs to have an external pull-up resistor connected to VCC1 (see application diagram in **Chapter 14**).

**Figure 4** shows the timing diagram of the hardware configuration selection. The hardware configuration is defined during SBC Init Mode. The INTN pin is internally pulled Low with a weak pull-down resistor during the reset delay time  $\mathbf{t}_{RD1}$ , i.e. after VCC1 crosses the reset threshold VRT1 and before the RSTN pin goes High. The INTN pin is monitored during this time (with a continuous filter time of  $\mathbf{t}_{CFG\_F}$ ) and the configuration (depending on the voltage level at INTN) is stored at the rising edge of RSTN.

Note:

If the **POR** bit is not cleared, then the internal pull-down resistor at INTN is reactivated every time RSTN is pulled Low the configuration is updated at the rising edge of RSTN. Therefore it is recommended to clear the **POR** bit right after initialization. In case there is no stable signal at INTN, then the last filtered value is taken. If no filtered value is taken then the default value '0' is taken as the config select value (= SBC Fail-Safe Mode).

Note:

During device power up, the SPI status bits **VCC1\_WARN**, **VCC1\_UV** and **VS\_UV** are updated only if RSTN is released after the reset delay time.

# infineon

### **System Features**

Figure 4 Hardware Configuration Selection Timing Diagram

There are four different device configurations (**Table 5**) available defining the watchdog failure and the VCC1 over voltage behavior. The configurations can be selected via the external connection on the INTN pin and the SPI bit **CFG1** in the **HW\_CTRL\_0** register (see also **Chapter 13.4**):

- CFG0\_STATE = '1': Config 1 and Config 3:

- A watchdog trigger failure leads to SBC Restart Mode and depending on CFG1 the Fail Output (FO) is activated after the 1st (Config 1) or 2nd (Config 3) watchdog trigger failure;

- A VCC1 over voltage detection leads to SBC Restart Mode if VCC1\_OV\_RST is set.

VCC1\_OV is set and the Fail Output is activated;

- CFG0\_STATE = '0': Config 2 and Config 4:

- A watchdog trigger failure leads to SBC Fail-Safe Mode and depending on CFG1 the Fail Output (FO) is activated after the 1st (Config 2) or 2nd (Config 4) watchdog trigger failure. The first watchdog trigger failure in Config 4 leads to SBC Restart Mode;

- A VCC1 over voltage detection leads to SBC Fail-Safe Mode if VCC1\_OV\_RST is set.

VCC1\_OV is set and the Fail Output is activated;

The respective device configuration can be identified by reading the SPI bit CFG1 in the HW\_CTRL\_0 register and the CFG0\_STATE bit in the WK\_LVL\_STAT register.

**Table 5** shows the configurations and the device behavior in case of a watchdog trigger failure:

# infineon

### **System Features**

Table 5 Watchdog Trigger Failure Configuration

| Config | INTN Pin<br>(CFG0_STATE) | SPI Bit<br>CFG1 | Event                       | FO Activation        | SBC Mode Entry                   |

|--------|--------------------------|-----------------|-----------------------------|----------------------|----------------------------------|

| 1      | External pull-up         | 1               | 1 x Watchdog Failure        | after 1st WD Failure | SBC Restart Mode                 |

| 2      | No ext. pull-up          | 1               | 1 x Watchdog Failure        | after 1st WD Failure | SBC Fail-Safe Mode               |

| 3      | External pull-up         | 0               | 1 & 2 x Watchdog<br>Failure | after 2nd WD Failure | SBC Restart Mode                 |

| 4      | No ext. pull-up          | 0               | 2 x Watchdog Failure        | after 2nd WD Failure | SBC Fail-Safe Mode <sup>1)</sup> |

<sup>1)</sup> SBC Restart Mode is entered after the 1. watchdog failure. The 2nd watchdog failure leads to SBC Fail-Safe Mode

**Table 6** shows the configurations and the device behavior in case of a VCC1 over voltage detection when **VCC1\_OV\_RST** is set:

Table 6 Device Behavior in Case of VCC1 Over Voltage Detection

| Config | INTN Pin<br>(CFG0_STATE) | CFG1<br>Bit | VCC1_O<br>V_RST | Event       | VCC1_<br>OV | FO Activation     | SBC Mode Entry     |

|--------|--------------------------|-------------|-----------------|-------------|-------------|-------------------|--------------------|

| 1-4    | any value                | х           | 0               | 1 x VCC1 OV | 1           | no FO activation  | unchanged          |

| 1      | External pull-<br>up     | 1           | 1               | 1 x VCC1 OV | 1           | after 1st VCC1 OV | SBC Restart Mode   |

| 2      | No ext. pull-up          | 1           | 1               | 1 x VCC1 OV | 1           | after 1st VCC1 OV | SBC Fail-Safe Mode |

| 3      | External pull-<br>up     | 0           | 1               | 1 x VCC1 OV | 1           | after 1st VCC1 OV | SBC Restart Mode   |

| 4      | No ext. pull-up          | 0           | 1               | 1 x VCC1 OV | 1           | after 1st VCC1 OV | SBC Fail-Safe Mode |

The respective configuration is stored for all conditions and can only be changed in SBC Init Mode, when RSTN is 'Low' or by powering down the device (VS  $< V_{POR,f}$ ) assuming the bit **POR** is cleared right after the device power up (see also not on **Page 20**).

# **System Features**

### 5.1.1.2 SBC Init Mode

In SBC Init Mode, the device waits for the microcontroller to finish its startup and initialization sequence.

The SBC starts with a long open watchdog window (see also Chapter 12.2).

All diagnosis functions which are enabled by default at device power-up are active.

While in SBC Init Mode any valid SPI command (from the SPI protocol, i.e. 16-bit word) sets the device to SBC Normal Mode, i.e. any register can be written, cleared and read. During the long open window the watchdog has to be triggered (i.e. thereby the watchdog is automatically configured).

A missing watchdog trigger during the long open window will cause a watchdog failure and the device will enter SBC Restart Mode.

Wake-up events are ignored during SBC Init Mode.

A SBC Soft Reset command (MODE = '11') sets the SBC back into SBC Init Mode and the SPI registers are changed to their respective Soft Reset values. In case one or both lock bits are set (CFG\_LOCK\_0 or CFG\_LOCK\_1) the locked bits keep their previous values and stay unchanged.

Note: Any SPI command sets the SBC to SBC Normal Mode even if it is an illegal SPI command (see

**Chapter 13.2**).

Note: For a safe start-up, it is recommended to use the first SPI command to trigger and to configure the

watchdog (see Chapter 12.2).

Note: At power up, the SPI bit  $VCC1_UV$  is not set nor is the FO triggered as long as VCC1 is below the  $V_{RT,x}$

threshold and VS is below the  $V_{s,uv}$  threshold. The RSTN pin is kept Low as long as VCC1 is below the selected  $V_{RT,x}$  threshold and the reset delay time is not expired. After the first threshold crossing (VCC1 > Vrt1,r) and the RSTN transition from Low to High, all subsequent undervoltage events lead

to SBC Restart Mode.

Note: The bit **VS\_UV** is updated only in SBC INIT Mode once RSTN resumes a high level.

# infineon

### **System Features**

### 5.1.2 SBC Normal Mode

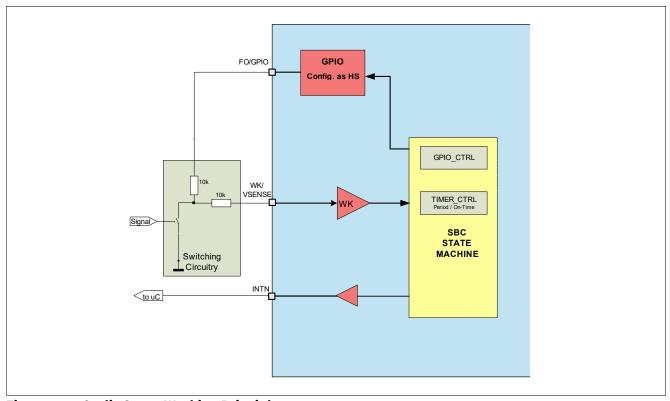

The SBC Normal Mode is the standard operating mode for the SBC. All remaining configurations must be done in SBC Normal Mode before entering a low-power mode (see also **Chapter 5.1.6**). A wake-up event on CAN, WK/VSENSE, FO/GPIO configured as wake input, the Timer will create an interrupt on pin INTN - however, no change of the SBC mode will occur. The configuration options are listed below:

- VCC1 is always active

- VCC2 can be switched On or Off (default = Off)

- CAN is configurable (it is Off coming from SBC Init Mode; Off or Wake Capable coming from SBC Restart Mode, see also Chapter 5.1.5)

- WK/VSENSE pin shows the input level and can be selected to be wake capable (interrupt), the alternative measurement function with the voltage output at FO/GPIO can be activated by setting WK\_MEAS

- Cyclic Sense can be configured with the HS function of the GPIO (GPIO = '011'), WK/VSENSE input and

Timer

- Cyclic Wake can be configured using the timer

- Watchdog period is configurable

- The Charge Pump Output can be switched On or Off (default = Off)

- The FO/GPIO output is inactive by default. Coming from SBC Restart Mode and configured as FO it can be

active (due to a failure event, e.g. watchdog trigger failure, VCC1 short circuit, etc.) or inactive (no failure

occurred)

- GPIO is configurable and is controlled by PWM; GPIO is Off coming from SBC Restart Mode

Certain SPI control bits with the bit type 'rwl' can be protected against unintentional modification by setting the  $CFG\_LOCK\_1$  bit in the register  $HW\_CTRL\_2$ . The locking mechanism stays activated until the device is powered down (VS <  $V_{POR,f}$ ). The charge pump and GPIO configuration can also be locked by setting the  $CFG\_LOCK\_0$  bit in the register  $HW\_CTRL\_1$ . The lock can be reset in SBC Normal Mode.

In SBC Normal Mode, the FO output can be tested within the system (i.e. to verify whether setting the FO/GPIO pin to Low creates the intended behavior). The FO output can be enabled and then disabled again by the microcontroller setting or resetting the **FO\_ON** SPI bit. This feature is only intended for testing purposes.

## **System Features**

### 5.1.3 SBC Stop Mode

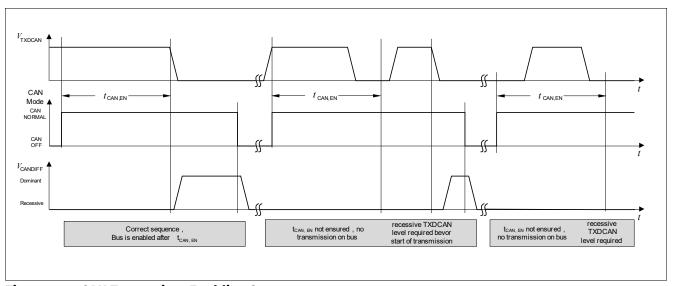

The SBC Stop Mode is the first level technique to reduce the overall current consumption by setting the voltage regulators VCC1, VCC2 into a low-power mode. In this mode VCC1 is still active, supplying the microcontroller, which can enter a power-down mode. The VCC2 supply can be configured to stay enabled and CAN to stay in Normal Mode. All settings have to be done before entering SBC Stop Mode. In SBC Stop Mode all SPI WRITE commands are ignored and the SPI\_FAIL bit is set. Exceptions are changing to SBC Normal Mode, triggering a SBC Soft Reset, refreshing the watchdog as well as reading and clearing the SPI status registers. A wake-up event on CAN, WK/VSENSE, FO/GPIO (if configured as wake input) and Timer create an interrupt on pin INTN - however, the SBC mode remains unchanged. The configuration options are listed below:

- VCC1 is always On

- VCC2 is fixed as configured in SBC Normal Mode

- CAN mode is fixed as configured in SBC Normal Mode

- WK/VSENSE pin is fixed as configured in SBC Normal Mode

- Cyclic Sense is fixed as configured in SBC Normal Mode

- Cyclic Wake is fixed as configured in SBC Normal Mode

- Watchdog is fixed as configured in SBC Normal Mode

- · SBC Soft Reset can be triggered

- The Charge Pump state is fixed as configured in SBC Normal Mode

- FO output works as configured in SBC Normal Mode unless it is changed by the software (i.e. by clearing the **FAILURE** bit and triggering the watchdog properly)

- · GPIO is fixed as configured in SBC Normal Mode

If not all wake source signalization flags from **WK\_STAT\_0** and **WK\_STAT\_1** are cleared before entering SBC Stop Mode, then an interrupt is triggered on the pin INTN.

Note: If outputs are kept enabled during SBC Stop Mode, e.g. HS of GPIO, then the SBC current

consumption increases respectively (see Chapter 4.4).

Note: It is not possible to switch directly from SBC Stop Mode to SBC Sleep Mode. Doing so sets the

**SPI\_FAIL** flag and SBC into Restart Mode is entered.

Note: When WK/VSENSE and FO/GPIO are configured for the alternative measurement function

(WK\_MEAS = 1) the pins cannot be selected as wake input sources.

## **System Features**

### 5.1.4 SBC Sleep Mode

The SBC Sleep Mode is the second level technique to reduce the overall current consumption to a minimum needed to react on wake-up events or for the SBC to perform autonomous actions (e.g. Cyclic Sense). In this mode, VCC1 is Off, not supplying the microcontroller anymore. The VCC2 supply can be configured to stay enabled. The settings have to be done before entering SBC Sleep Mode. A wake-up event on CAN, WK/VSENSE, FO/GPIO (if configured as wake input) and the internal Timer brings the device via the SBC Restart Mode subsequently to SBC Normal Mode again and signals the wake source.

The configuration options are listed below:

- VCC1 is always Off

- VCC2 is fixed as configured in SBC Normal Mode

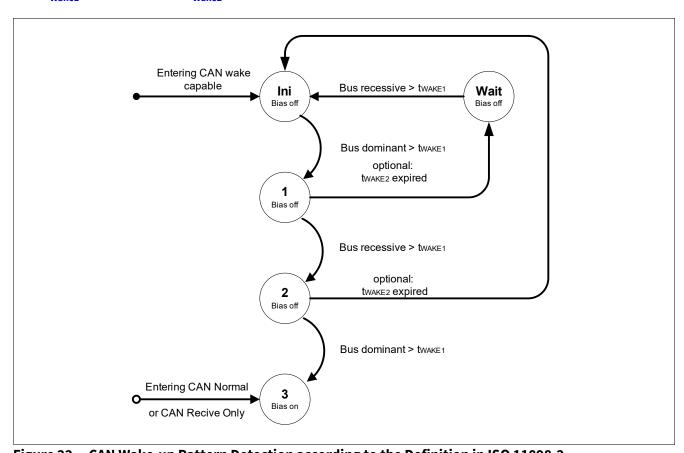

- CAN mode changes automatically from On or Receive Only Mode to Wake Capable mode or can be selected

to be Off

- WK/VSENSE pin is fixed as configured in SBC Normal Mode

- Cyclic Sense is fixed as configured in SBC Normal Mode

- Cyclic Wake is fixed as configured in SBC Normal Mode, it can be the only activated wake source

- · Watchdog is Off

- The Charge Pump state is fixed as configured in SBC Normal Mode

- FO output is fixed as configured in SBC Normal Mode is maintained

- GPIO is fixed as configured in SBC Normal Mode, it can be the only wake source if configured as WK/VSENSE

- RSTN is pulled low

- SPI communication and all digital I/Os are disabled because VCC1 is Off

- The Sleep Mode entry is signalled in the SPI register DEV\_STAT with the bit DEV\_STAT

It is not possible to switch Off all wake sources in SBC Sleep Mode. Doing so sets the **SPI\_FAIL** flag and the device enters SBC Restart Mode.

In order to enter SBC Sleep Mode successfully, all wake source signalization flags from **WK\_STAT\_0** and **WK\_STAT\_1** need to be cleared. A failure to do so results in an immediate wake-up from SBC Sleep Mode by going via SBC Restart to Normal Mode.

All settings must be done before entering SBC Sleep Mode.

Note: If outputs are kept enabled during SBC Sleep Mode, e.g. HS of GPIO, then the SBC current

consumption increases respectively (see Chapter 4.4).

Note: The Cyclic Sense function might not work properly anymore in case of a failure event (e.g.

overcurrent, over temperature, reset) because the configured HS of the GPIO and Timer might be

disabled.

Note: When WK/VSENSE and FO/GPIO are configured for the alternative measurement function

(WK\_MEAS = 1) then the pins cannot be selected as wake input sources.

# infineon

### **System Features**

### 5.1.5 SBC Restart Mode

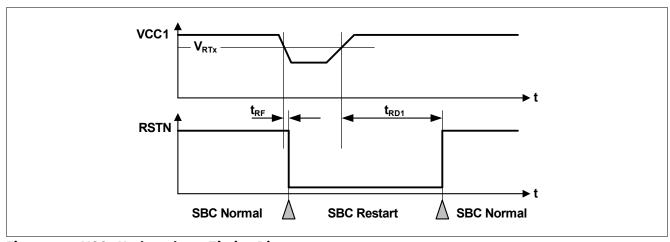

There are multiple reasons to enter the SBC Restart Mode. The main purpose of the SBC Restart Mode is to reset the microcontroller:

- in case of under voltage at VCC1 in SBC Normal and SBC Stop Mode and SBC Init Mode after RSTN has been released,

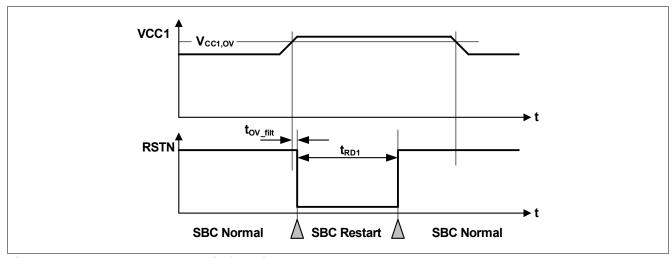

- in case of over voltage at VCC1 (if the bit VCC1\_OV\_RST is set and if CFG0\_STATE = '1'),

- due to 1st incorrect Watchdog triggering (only if Config1, Config3 or Config 4 is selected, otherwise SBC Fail-Safe Mode is immediately entered),

- In case of a wake event from SBC Sleep or Fail-Safe Mode or a release of over temperature shutdown (TSD2) out of SBC Fail-Safe Mode (this transition is used to ramp up VCC1 in a defined way).

From SBC Restart Mode, the device enters automatically to SBC Normal Mode. The SBC MODE bits are cleared. As shown in Figure 32 the Reset Output (RSTN) is pulled Low when entering Restart Mode and is released (going High) at the transition to SBC Normal Mode after the reset delay time (t<sub>RD1</sub>). The watchdog timer starts with a long open window starting from the moment of the rising edge of RSTN. The watchdog period settings in the register WD\_CTRL are changed to the respective default value '100'.

Leaving the SBC Restart Mode does not result in changing / deactivating the Fail Output.

The behavior of the blocks is listed below:

- FO (if configured as FO) is activated in case of a 1st watchdog trigger failure (Config1) or a 2nd watchdog failure (Config3) or in case of VCC1 over voltage detection (if VCC1\_OV\_RST is set)

- VCC1 stays On or is ramping up (coming from SBC Sleep or Fail-Safe Mode)

- VCC2 is disabled if it was activated before

- CAN is "woken" due to a wake-up event or Off depending on the previous SBC and transceiver mode (see also Chapter 8). It is Wake Capable when it was in CAN Normal-, Receive Only or Wake Capable mode before SBC Restart Mode

- GPIO behavior: switched Off if configured as LS- or HS-switch, see also Chapter 11.1.2

- RSTN is internally pulled Low during SBC Restart Mode

- SPI communication is ignored by the SBC, i.e. it is not interpreted

- The SBC Restart Mode entry is signalled in the SPI register DEV\_STAT with the bits DEV\_STAT

Table 7 Reasons for Restart - State of SPI Status Bits (after Return to SBC Normal Mode)

| Prev. SBC Mode | Event                    | DEV_STAT | WD_FAIL    | VCC1_UV       | VCC1_OV               | VCC1_SC |

|----------------|--------------------------|----------|------------|---------------|-----------------------|---------|

| Normal         | 1x Watchdog Failure      | 01       | 01         | х             | х                     | Х       |

| Normal         | 2x Watchdog Failure      | 01       | 10         | х             | х                     | Х       |

| Normal         | VCC1 under voltage reset | 01       | XX         | 1             | х                     | х       |

| Normal         | VCC1 over voltage reset  | 01       | XX         | х             | 1                     | Х       |

| Stop           | 1x Watchdog Failure      | 01       | 01         | х             | х                     | х       |

| Stop           | 2x Watchdog Failure      | 01       | 10         | х             | х                     | Х       |

| Stop           | VCC1 under voltage reset | 01       | XX         | 1             | х                     | Х       |

| Stop           | VCC1 over voltage reset  | 01       | XX         | х             | 1                     | х       |

| Sleep          | Wake-up event            | 10       | XX         | х             | х                     | х       |

| Fail-Safe      | Wake-up event            | 01       | see "Reaso | ns for Fail S | afe, <b>Table 8</b> ' | ,       |

### **System Features**

Note: An over voltage event at VCC1 leads to SBC Restart Mode only if the bit VCC1\_OV\_RST is set and if

**CFG0\_STATE** = '1' (Config 1/3).

Note: The content of the WD\_FAIL bits depends on the device configuration, e.g. 1 or 2 watchdog failures.

### 5.1.6 SBC Fail-Safe Mode

The purpose of this mode is to bring the system in a safe status after a failure condition by turning Off the VCC1 supply and powering Off the microcontroller. After a wake-up event the system restarts again.

The Fail-Safe Mode is automatically entered after following events:

- SBC thermal shutdown (TSD2) (see also Chapter 12.8.3),

- over voltage on VCC1 if the bit VCC1\_OV\_RST is set and if CFG0\_STATE = '0',

- 1st incorrect watchdog trigger in Config2 (CFG1 = 1) and after a 2nd incorrect watchdog trigger in Config4 (CFG1 = 0) (see also Chapter 5.1.1),

- VCC1 is shorted to GND (see also Chapter 12.6),

In this case, the default wake sources CAN, WK/VSENSE and FO/GPIO (if configured as wake input - see also registers **BUS\_CTRL\_0**, **WK\_CTRL\_1** and **GPIO\_CTRL**) are activated, the previous wake-up events are cleared in the register **WK\_STAT\_0** and **WK\_STAT\_1**, and both voltage regulators and the GPIO - if configured as HS or LS - are switched Off.

The SBC Fail-Safe Mode is entered regardless of the FO/GPIO pin configuration. If WK/VSENSE and FO/GPIO are configured for the alternative measurement function (**WK\_MEAS** = 1) then these pins keep their configuration for the measurement function when SBC Fail-Safe Mode is entered, i.e. they are not automatically activated as wake sources.

The SBC Fail-Safe Mode is maintained until a wake-up event on the default wake sources occurs. To avoid any fast toggling behavior a filter time of typ. 100ms ( $t_{FS,min}$ ) is implemented. Wake-up events during this time is stored and automatically lead to SBC Restart Mode after the filter time.

In case of a VCC1 over temperature shutdown (TSD2), the SBC Restart Mode is entered automatically after a filter time of typ. 1s (t<sub>TSD2</sub>) (without the need of a wake-up event) once the device temperature has fallen below the TSD2 threshold. Please see **Chapter 12.8.3** on how to extend the minimum TSD2 waiting time. Leaving the SBC Fail-Safe Mode does not result in a deactivation of the Fail Output pins.

The following functions are controlled by the C Fail-Safe Mode:

- FO output (if configured as FO) is activated (see also Chapter 11)

- VCC1 is switched Off

- VCC2 is switched Off

- CAN is set to Wake Capable

- GPIO behavior:

- if configured as HS or LS: it is switched Off

- if configured as wake input: it is set to wake capable in Static Sense mode

- WK/VSENSE pin is set to wake capable in Static Sense mode (only if WK\_MEAS = 0)

- Cyclic Sense and Cyclic Wake is disabled

- SPI communication is disabled because VCC1 is Off, RSTN and digital I/O pins are pulled Low

- The Fail-Safe Mode activation is signalled in the SPI register DEV\_STAT with the bits FAILURE and DEV\_STAT

# infineon

### **System Features**

Table 8 Reasons for Fail-Safe - State of SPI Status Bits after Return to Normal Mode

| Prev. SBC<br>Mode | Failure Event        | DEV_<br>STAT | TSD2 | WD_<br>FAIL | VCC1_<br>UV | VCC1_<br>OV | VCC1_<br>SC |

|-------------------|----------------------|--------------|------|-------------|-------------|-------------|-------------|

| Normal            | 1 x Watchdog Failure | 01           | х    | 01          | х           | х           | х           |

| Normal            | 2 x Watchdog Failure | 01           | х    | 10          | х           | х           | х           |

| Normal            | TSD2                 | 01           | 1    | xx          | х           | х           | х           |

| Normal            | VCC1 short to GND    | 01           | х    | xx          | 1           | х           | 1           |

| Normal            | VCC1 over voltage    | 01           | х    | xx          | х           | 1           | х           |

| Stop              | 1 x Watchdog Failure | 01           | х    | 01          | х           | х           | х           |

| Stop              | 2 x Watchdog Failure | 01           | х    | 10          | х           | х           | х           |

| Stop              | TSD2                 | 01           | 1    | xx          | х           | х           | х           |

| Stop              | VCC1 short to GND    | 01           | х    | xx          | 1           | х           | 1           |

| Stop              | VCC1 over voltage    | 01           | х    | xx          | х           | 1           | х           |

Note: An over voltage event on VCC1 leads to SBC Fail-Safe Mode only if the bit VCC1\_OV\_RST is set and if **CFGO\_STATE** = '0' (Config 2/4).

Note: The content of the WD\_FAIL bits depends on the device configuration, e.g. 1 or 2 watchdog failures.

## 5.1.7 SBC Development Mode

The SBC Development Mode is used during the development phase of the module. It is especially useful for software development.

Compared to the default SBC user mode operation, this mode is a super set of the state machine. The device starts also in SBC Init Mode and it is possible to use all the SBC Modes and functions with the following differences:

- Watchdog is stopped and does not need to be triggered. Therefore no reset is triggered due to watchdog failure

- SBC Fail-Safe and SBC Restart Mode are not activated by a watchdog trigger failure (but the other reasons to enter these modes are still valid)

- CAN and VCC2 default values in SBC Init Mode and if entering SBC Normal Mode from SBC Init Mode is On (instead of Off)

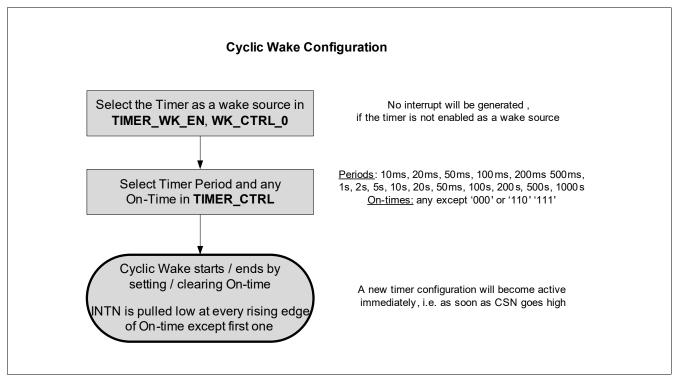

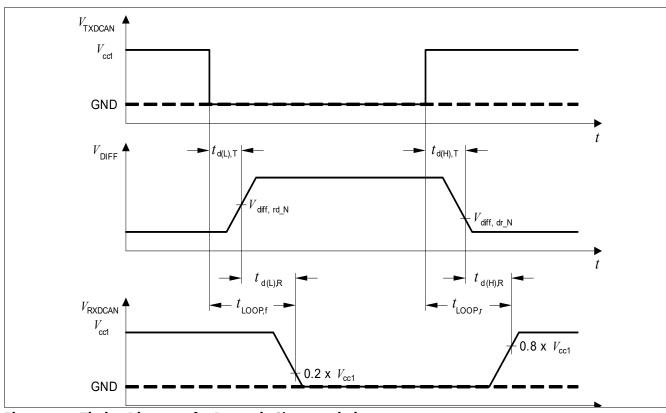

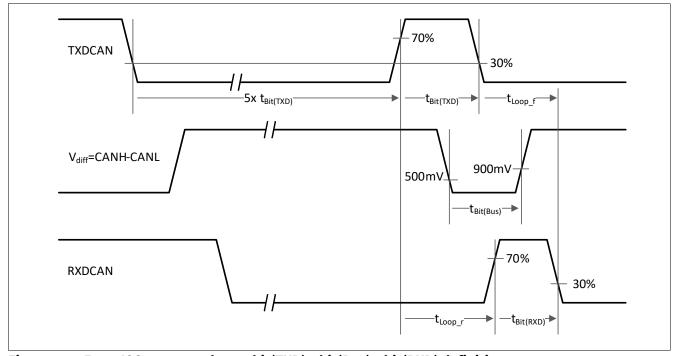

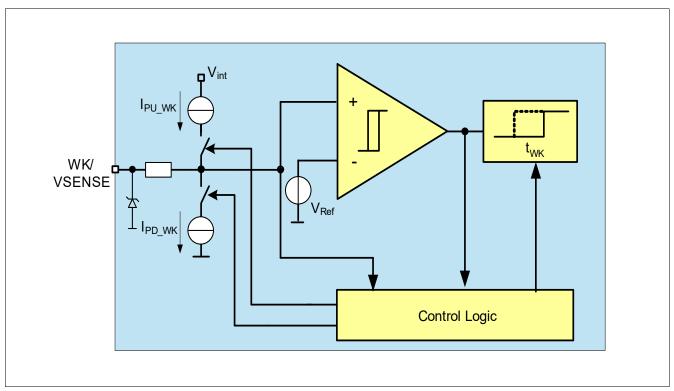

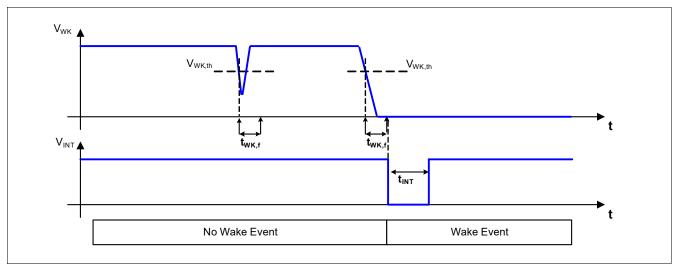

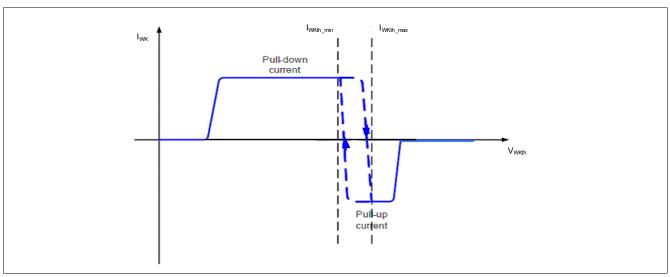

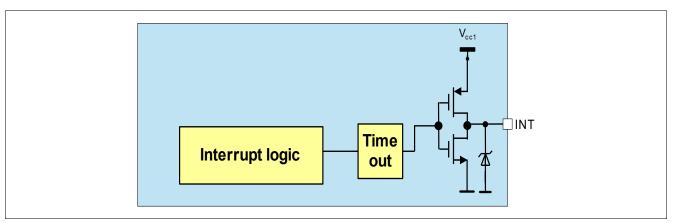

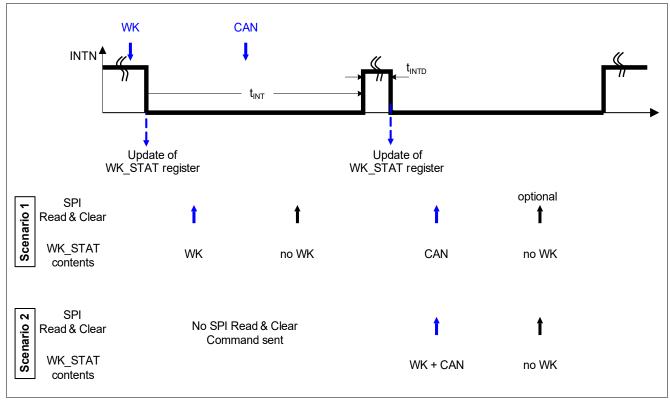

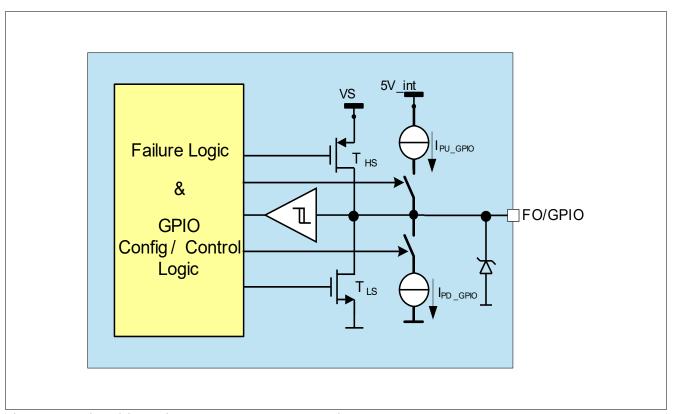

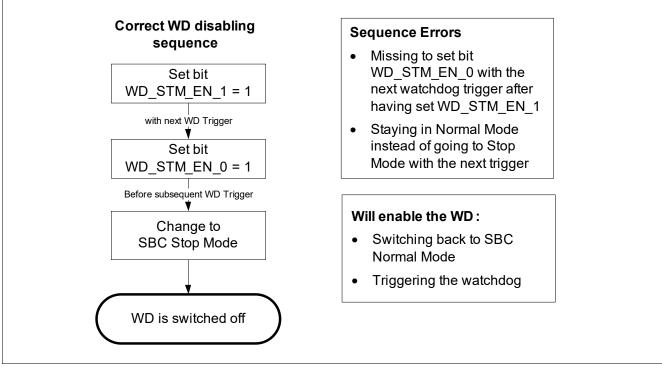

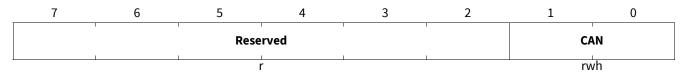

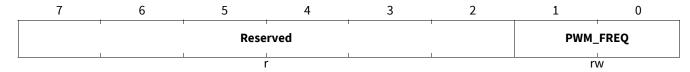

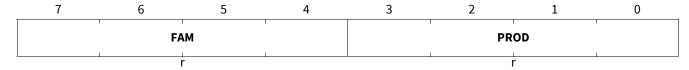

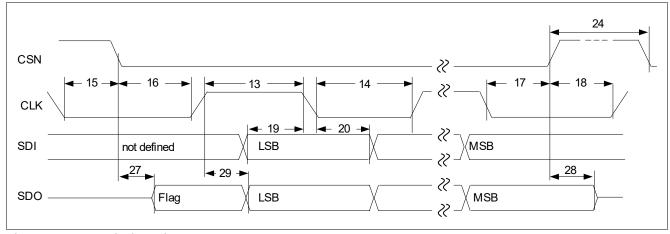

The SBC Development Mode is entered automatically, if the TEST pin is set High (i.e. connected to VCC1 with (5V level) during SBC Init Mode. The voltage level monitoring is started as soon as VS > V<sub>POR,r</sub> and VCC1 > V<sub>RT1,r</sub>. The SBC Development Mode is set and maintained, if SBC Init Mode is left by sending any SPI command while TEST is High. The bit SBC\_DEV\_LVL shows the status of the SBC Development Mode.